# A MODIFIED ARCHITECTURE DESIGN FOR ADVANCE ENCRYPTION STANDARD WITH ENHANCEMENT IN MIX COLUMNS FOR SECURE DATA USAGE

## Gadagottu Jyosthna<sup>1</sup>, L.Srinivas Reddy<sup>2</sup>

<sup>1</sup> M.Tech (VLSI) Scholar, Nalanda Institute of Engg. and Tech.(NIET), Siddharth Nagar, Guntur, A.P. (India) <sup>2</sup> Asst. Professor (ECE) from Nalanda Institute of Engg and Tech.(NIET), Siddharth Nagar, Guntur, A.P. (India)

#### **ABSTRACT**

In this paper we are presenting an encryption algorithm called Advance Encryption Standard . We have designed AES algorithm using Verilog HDL and in this design we have used look up table substitution for byte in state matrix, also for low complexity and low latency hardware for efficient performance. This design was simulated in Xilins ISE 13.2, compared results with previous design performances.

Keywords: AES, Cipher, Shiftrows, Mix Columns, Lookup Table, ROM

## I. INTRODUCTION

In earlier days Data encryption standard (DES) was considered as encryption standard with symmetrical key encryption with the keysize of 56 bits. After certain days 56 bit key was considered to be small and for high data bit systems require key and data size to be large. In the year 1990 the National institute of standards call for papers on new encryption methods. So many researchers sent their papers to NIST, out of allthose few were selected for testing. Cryptographic researchers after performing test on them only five are best among them ,those are Mars, RC6, Rijndael, Serpent and Twofish. These five went onto further testing afterperforming these tests they have declared that Rijndael algorithm was the winner. According this AES algorithm data and key size may be any size i.e muiltiple of 32 bits, with minimunm of 128bits and maximum of 256 bits. This algorithm also called Rijndael algorithm of AES. AES can be implemented in software and hardware. Software implementation require less resources and cost and its implicablity also limited ,having low seed. Nowadays we require large volume data and high speed requirements made it to implement ain hardware. Hard ware nothing but we have application specific IC and FPGA. FPGA is reconfigurable device which supports wide range of functionality than ASIC. So we prefer FPGAS to implement AES.

## II. AES ALGORITHM

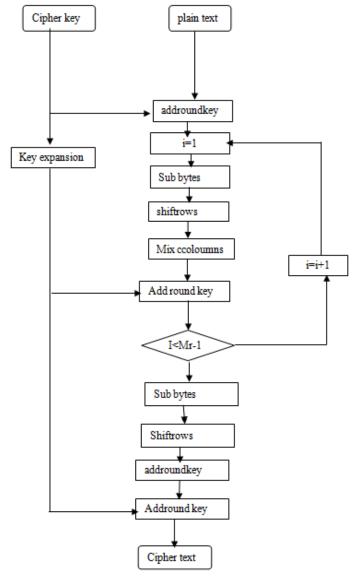

AES algorithm is using for encrypting the data and for decrypting the data. Encryption is nothing but converting data into unknown format called cipher text. Decryption iis converting the cipher into normal text called plain text. In AES we are using 128 bit block and data and keys.we will perform  $M_r$  number of iterations each

iteration is called as loop.  $M_r$  denotes number of loops.this may be depend upon the key size that may be 10, 12 or 14 with respective of size of key is 128,192,256. First we will discuss about Encryption later then decryption

## 2.1 Aes Encryption

As we discussed earlier it will operate on the 128bit block size of data and key. This is having following stages addroundkey, substitution byte, shiftrows, mix columns, are repeated in loop format depending upon of our key size. They key can can be used for every loop is different and is derived from the original key, for that we have a key exapansion algorithm. This algorithm will generate different keys for all rounds.

The proposed AES is similar to the conventional AES but the difference is in construction of S-box which was made by combinational gates. AES algorithm works on 4\*4 matrix element called states. It works on states which is of 8bit length.

The state will undergo following stages namely sub bytes and inverse sub bytes, shift rows, and mix columns, transformations. The AES algorithm represented pictorially as below

## 2.1.1 Subbytes

This is a nonlinear transformation each byte in the state matrix was replaced by the precalculated data called substation box S-box. This s-box was precalculated stored in the rom called look up table. This method of implementation will reduce the latency and more promionently can be implemented in single clock cycle

## 2.1.2 Shiftrows

This stage having shifting of state rows cyclically leftside. That means each row is shifted by some offset, first row is unchanged, second row shifted by one bit, third row shifted by two bits, last row shifted by three bits.

Figure 2.1 Shiftrows

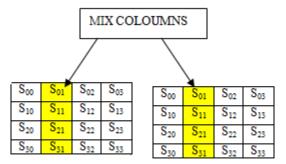

## 2.1.3 Mix Coloumns

In this stage columns in the state matrix was considered as polynomial over galois field. This polynomial is multiplied by the modulo  $X^4+1$  with a fixed polynomial d(x).

Figure 2.2 Mix Columns

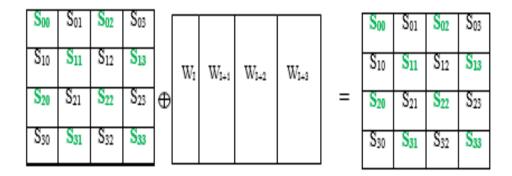

## 2.1.4 Addroundkey

In this round state byte is added to the key which was derived from main key. This addition is modulo addition or xor ing the key with byte. This may be happen in 10 or 12 rounds, for each round new key is used.

## 2.2 AES Decryption

This is simply reverse process to the encryption algorithm which converts cipher text to plain text i.e to readle format. It uses exactly inverse algorithm used for encryption.

## 2.2.1 Add Round Key

In this stage we are performing modulo 2addition or xor operation with the sub byte. Xor operation is self inverse so we will again perform same operation but keys are selected in reverse order.

## 2.2.2 Inv Shiftrows

Figure 2.3 Inv Shift Rows

In this round exactly reverse process for the shift rows were performed i.e firstrow will not be alterd, second and third and final rows are shift by one ,two ,and three positions respectively.

## 2.2.3 Inv Subbyte

In this round the byte which was result of previous operations was replaced according to the precalculated inv sub byte table called inv s-box table. This table has all the values from 0 to 256 and their respective replacement data. According to that data it will be transformed.

## 2.2.4 Inv Mix Columns

In this round polynomial of state matrix over galois field, which are having degree less than 4 are coefficients of state are multiplied with modulo X4+1 and with a fixed polynomial  $e(x) = \{0B\}x^3 + \{0D\}x^2 + \{09\}x + \{0E\}$ . enhances the performance and throughput of encryption at faster rate.

|   |   | Y  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | а  | b  | C  | d  | e  | f  |

|   | 0 | 63 | 7¢ | 77 | 7b | F2 | 6b | 6f | C5 | 30 | 1  | 67 | 2b | fe | D7 | ab | 76 |

|   | 1 | Ca | 82 | C9 | 7d | Fa | 59 | 47 | F0 | ad | D4 | A2 | af | 90 | Α4 | 72 | CO |

|   | 2 | 87 | Fd | 93 | 26 | 36 | 3f | F7 | Cc | 34 | A5 | E5 | F1 | 71 | D8 | 31 | 15 |

| x | 3 | 4  | 07 | 23 | C3 | 18 | 96 | 5  | 9a | 7  | 12 | 80 | E2 | eb | 27 | B2 | 75 |

|   | 4 | 9  | 83 | 20 | 1a | 1b | бе | 5a | AO | 52 | 3b | D6 | B3 | 29 | E3 | 2f | 84 |

|   | 5 | 53 | D1 | 0  | Ed | 20 | FC | 81 | 5b | ба | Cb | Ве | 39 | 4a | 4c | 58 | ď  |

|   | 6 | D0 | Ef | Aa | Fb | 43 | 4d | 33 | 85 | 45 | F9 | 2  | 7f | 50 | 3c | 9f | AS |

|   | 7 | 51 | A3 | 40 | 8f | 92 | 9d | 38 | F5 | Вс | 86 | da | 21 | 10 | ff | F3 | 02 |

|   | 8 | Cd | Oc | 13 | Ec | 5f | 97 | 44 | 17 | C4 | A7 | 7e | 3d | 64 | 5d | 19 | 73 |

|   | 9 | 60 | 81 | 4f | Dc | 22 | 29 | 90 | 88 | 45 | Ee | B8 | 14 | de | 5e | 0b | db |

|   | a | EO | 32 | 3a | 0a | 49 | 6  | 24 | 5c | C2 | D3 | Ac | 62 | 91 | 95 | E4 | 79 |

|   | b | E7 | C8 | 37 | 6d | 8d | D5 | 4e | A9 | 60 | 56 | F4 | ea | 65 | 7a | ae | 8  |

|   | ¢ | Ва | 78 | 25 | 2e | 10 | A6 | B4 | C6 | E8 | Dd | 74 | 1f | 4b | bd | 86 | 88 |

|   | d | 70 | 3е | B5 | 66 | 48 | 3  | F6 | 0e | 61 | 35 | 57 | ba | 86 | а  | 1d | 9e |

|   | 6 | E1 | F8 | 98 | 11 | 69 | D9 | 8e | 94 | 9b | 1e | 87 | ca | œ  | 55 | 28 | df |

|   | f | SC | A1 | 89 | 0d | bf | E6 | 42 | 68 | 41 | 99 | 2d | Of | В0 | 54 | bb | 16 |

|   |   | *  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 8  | b  | C  | d  | ē  | f  |

|   | 0 | 52 | 9  | 6a | 05 | 30 | 36 | A5 | 38 | bf | 40 | A3 | 9é | 81 | F3 | 07 | fb |

|   | 1 | 70 | E3 | 39 | 82 | 96 | 2f | Ff | 87 | 34 | 8e | 43 | 44 | (4 | de | E9 | d  |

|   | 2 | 54 | 7b | 94 | 32 | A5 | 02 | 23 | 3d | ee | 4c | 95 | Ob | 42 | fa | C3 | 46 |

|   | 3 | 8  | 2e | A1 | 66 | 28 | D9 | 24 | 82 | 76 | 50 | A2 | 49 | 6d | 8b | M  | 2  |

|   | 4 | 72 | F8 | F6 | 64 | 86 | 68 | 98 | 16 | D4 | A4 | 50 | CC | 5d | 65 | 86 | 9  |

| 1 | 5 | 60 | 70 | 48 | 50 | Fd | Ed | 89 | da | 5e | 15 | 46 | 57 | A7 | 86 | 9d | 8  |

| 1 | 6 | 90 | 08 | Ab | 0  | 80 | Вс | 08 | Oa | F7 | E4 | 58 | 5  | 88 | 83 | 45 | 6  |

|   | 7 | DO | 2c | 1e | 8f | Ca | 3f | Of | 2  | CI | 析  | bd | 3  | 1  | 13 | 88 | 6  |

| X | 8 | 3a | 91 | 11 | 41 | 4f | 67 | Dc | 68 | 97 | F2 | ď  | ce | FO | 84 | E6 | 7. |

| 1 | 9 | 96 | Ac | 74 | 22 | E7 | Ad | 35 | 85 | E2 | F9 | 37 | E8 | 1c | 75 | ď  | 6  |

|   | 3 | 47 | F1 | 1a | 71 | 10 | 29 | CS | 89 | 61 | 87 | 62 | 0e | 86 | 18 | be | 1  |

|   | b | Fc | 56 | Зе | 4b | C5 | D2 | 79 | 20 | 9a | Db | 00 | fe | 78 | cd | 5a | F  |

|   | t | 1f | Dd | A8 | 33 | 88 | 7  | 07 | 31 | 81 | 12 | 10 | 59 | 27 | 80 | ec | 5  |

|   | đ | 60 | 51 | 77 | A9 | 19 | 85 | 4a | Od | 2d | E5 | 7a | 9f | 93 | C9 | 90 | E  |

|   | e | A0 | EO | 3b | 4d | ae | 2a | F5 | 80 | 08 | Eb | bb | 30 | 83 | 53 | 99 | 6  |

|   | f | 17 | 2b | 4  | e  | ba | 77 | 06 | 26 | El | 69 | 30 | 63 | 55 | 21 | Θc | 7  |

Fig 2.4 S-Box Look Up Table

Fig 2.5 Inverse S-Box Look Up Table

Fig 2.6 AES Flow Chart

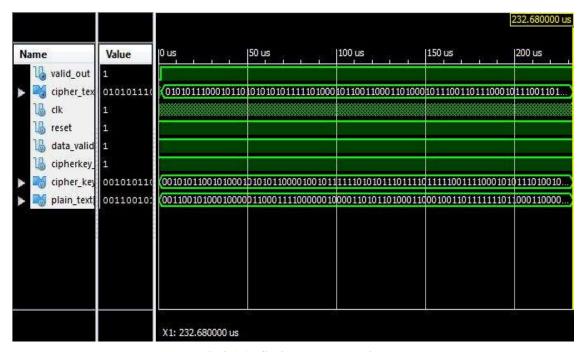

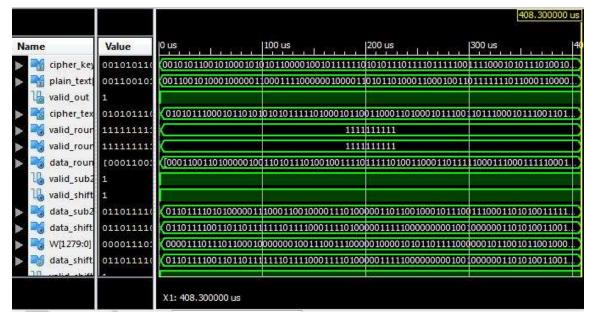

#### III. SIMULATION RESULTS

Here we have designed AES using Verilog HDL, we have given byte of data as input to the subbyte transformation stage. We designed sub byte as a precalculated table is lookup table and is stored in ROM. From that look up table we will select the input data and replace it with the respective byte in such way every round was designed and synthesised using Xilinx ISE 13.2. The synthesis reports will giving us this type of AES design has less delay compared to the combinational design of s-box.

Fig 3.1 AES with Key generation

Fig 3.2 AES with output generation

#### IV.CONCLUSION

We have designed a symmetric block cipher with 128 bit data and key sizes which has encryption and decryption round s may vary from 10, 12 or 14 rounds depend upon the key size. We have designed an AES algorithm which is having lesser delay and low complexity in hardware structure. This design enhances the

performance amd throughput of the AES. This was designed using Verilog HDL and this design was synthesized in the Xinix ISE13.2 and we have found that it is giving enhanced performance with lesser delay.

## V. REFERENCES

- [1] An efficient FPGA implementation of the Advanced Encryption Standard algorithm Hoang Trang, NaNguyen Van Loi.

- [2] Daemen J., and Rijmen V, "The Design of Rijndael: AES-the Advanced Encryption Standard", Springer-Verlag, 2002

- [3] Daemen J., and Rijmen V, "The Design of Rijndael: AES-the Advancedm Encryption Standard", Springer-Verlag, 2002

## **AUTHOR DETAILS**

GADAAGOTTU JYOSTHNA pursuing M.tech (VLSI) from the Nalnda institute of Engineering and Technology(NIET), Siddhrath nagar,Kantepudi village, Satenpalli Mandal, Guntur dist, A.P, India. Her area of interest includes cryptographic application of VLSI

**L.SRINIVAS REDDY**, He completed his post graduation in DECS. His area of interest includes digital electronics, digital communication, digital system design and VLSI technology and design. His research areas are optimal communication technology. He is currently working as Asst.professor (ECE) from Nalanda institute of Engineering and Technology (NIET), Siddharth Nagar, Kantepudi village, Satenepalli Mandal. Guntur Dist., A.P,