Vol. No.4, Issue No. 09, September 2016 www.ijates.com

# A NEW EFFICIENT APPROACH FOR DESIGN OF CDMA ENCODING BY USING MODIFIED WALSH/SB METHODS FOR ON CHIP COMMUNICATIONS

## Medikonda Ramakrishna<sup>1</sup>, D. Suneel<sup>2</sup>

<sup>1</sup>Pursuing M.tech from Nalanda Institute of Engineering and Technology(NIET), Siddharth Nagar, Kantepudi village, Sattenepalli Mandal Guntur Dist., A.P. INDIA

<sup>2</sup>Working as Asst.professor (ECE) from Nalanda Institute of Engineering and Technology(NIET), Siddharth

Nagar, Kantepudi village, Sattenepalli Mandal Guntur Dist., A.P. INDIA

#### **ABSTRACT**

As an elite on-chip specialized strategy, the code division various access (CDMA) method has as of late been connected to systems on chip (NoCs). We propose another standard-basis based encoding/deciphering strategy to influence the execution and expense of CDMA NoCs in range, power suspicion, and system throughput. In the transmitter module, source information from various senders are independently encoded with an orthogonal code of a standard premise and these coded information are combined by a XOR operation. At that point, the entireties of information can be transmitted to their goals through the onchipcorrespondence base. In the collector module, a succession of chips is recovered by taking an AND operation between the entireties of information what's more, the relating orthogonal code. After a basic aggregation of these chips, unique information can be remade. We execute our encoding/interpreting technique and apply it to a CDMA NoC with a star topology.

Keywords: CDMA encoding, Walsh, basis, orthogonal code.

#### I. INTRODUCTION

With the quick development of the computational unpredictability, progressively and additional handling components (PEs) are coordinated onto a solitary chip, also, arrange on chip (NoC) has been proposed to address the versatility, throughput, and unwavering quality issues of on-chip correspondence. Be that as it may, customary bundle changed NoCs experience the ill effects of nondeterministic transmission dormancy and restricted open doors for parallel information exchange, since numerous streams can't traverse a connection at the same time [1]. To determine these issues, the CDMA strategy [2] as a successful strategy for actualizing superior on-chip correspondence [3] was connected to NoCs [4], [5]. The already proposed CDMA NoCs depend on an advanced encoding and translating strategy requiring that the spreading codes have both the orthogonal and parity properties. To this end, the Walsh code is commonly utilized. In any case, the Walsh-code-based (WB) encoding and interpreting technique has characteristic weaknesses, which are given as takes after.

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

ISSN 2348 - 7550

- 1) Design Complexity: In the encoding strategy, a number juggling expansion rationale unit, whose rationale overhead increments with the number of senders, is utilized to combine coded information. In the interpreting technique, a key demux-amassing think about unit is used to recover the source information from blended information chips (in this brief, every piece of a spreading code is known as a chip, and in this manner the encoded information is called information chips). This unit is, in any case, territory expending.

- 2) Low Code Utilization: In a S-chip Walsh code set [6], S must be equivalent to 2N, where N is a characteristic number, and at most S 1 arrangements can be utilized to encode the first information. This brings about a misuse of groupings in the code set. For instance, a 16-hub arrange needs a 32-chip Walsh code set, on the grounds that a 16-chip Walsh code set can just give 15 arrangements to information encoding and it along these lines can't fulfil the necessity of 16 arrangements, one for every hub

#### II. RELATED WORK

To address the previously mentioned shortcomings, we propose a new standard-premise Based (SB) encoding/unraveling technique, which beats the WB encoding/disentangling strategy. The SB encoding/ unraveling technique can be connected to any CDMA NoCs to make strides their execution The CDMA method has as of late pulled in exploration considerations in the NoC people group. To demonstrate the benefits of CDMA NoC, Kim et al. [4] utilized Walsh codes to recognize distinctive senders and build up a various leveled star-network topology to handle a huge number of correspondence processors. The recreation comes about demonstrate that the CDMA NoC has great execution in inactivity and throughput. In [7], a particular application is planned onto a CDMA-based NoC and a customary crossbar-based bundle exchanged NoC. The trial comes about demonstrate that the CDMA NoC accomplishes lower bundle exchange idleness and less range overhead. To encourage enhance the CDMA NoC execution, a comprehensively offbeat locally synchronous (GALS) CDMA NoC is displayed furthermore, reenacted in [8]. By applying the GALS technique to CDMA NoC, the CDMA NoC can be utilized for offbeat chips. In [9], the multicasting capacity is acknowledged in CDMA NoC to address the hotspot issue at the focal point of NoC with lattice topology. The comes about show that movement clog at the focal point of NoC is decreased. Since code usage rate influences the CDMA NoC execution, two techniques on code word task are independently proposed in [10] and [11]. In [10], the length of code word is balanced contingent upon the quantity of hubs that have parcels to send at the same time. In [11], a booking technique is proposed to make a bargain on the usage rate of code words. Reenactment comes about demonstrate that these techniques enhance the usage productivity of the orthogonal codes. Other than the customary wired NoC, the CDMA system has moreover been connected to photonic NoC [12] and remote NoC [13]. The outcomes demonstrate that their execution can be altogether enhanced with lower vitality and territory contrasted and the crossbar-based NoC

### III. PROPOSED ENCODING AND DECODING METHODS

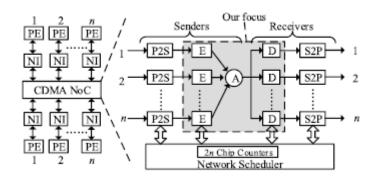

All the previously mentioned CDMA NoCs utilize the WB encoding/ deciphering technique, and along these lines they have the disadvantages said in Section I. Our proposed SB encoding/deciphering technique might beat the regular shortcomings The fundamental structure of applying CDMA method to NoC with a star topology is appeared in Fig. 1. In this figure, a PE executes undertakings of the application and system interface (NI)

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

**ijates** ISSN 2348 - 7550

separates information streams from PE into bundles and reproduce information streams by utilizing parcels from NoC.

In the sender, bundle flutters from NI are changed to a consecutive bit stream by means of a parallel-to-serial (P2S) module. This bit stream is encoded with an orthogonal code in the Encoding module (E in Fig. 1). The coded information from various encoding modules are included in the Addition module (An in Fig. 1). At that point, the aggregates of information chips are transmitted to recipients. In the collector, Decoding modules (D in Fig. 1) recreate unique information bits from the aggregates of information chips. At that point these consecutive piece streams are changed to bundle flutters by serial-to-parallel (S2P) modules. At last, these bundle bounces are exchanged to NI. In the CDMA NoC, system scheduler gets the transmitting demands from senders and allocates appropriate spreading codes to the senders and asked for beneficiaries. Note that every one of the zero codeword is alloted to hubs having no information to transmit/ get. Also, when there are numerous senders asking for the same collector, the scheduler will apply an assertion plan, for instance, round-robin. The chip counters ascertain what number of orthogonal chips are utilized as a part of one encoding/disentangling operation. Each hub needs two chip counters, one for the sender and the other for the collector. Note that parcel bounces from NI can likewise be changed to various piece streams in the P2S module to make tradeoffs between power/region expense and bundle exchange dormancy, and the scheduler ought to give somewhat synchronous plan to keep up the orthogonality of the transmitted channels, as talked about in [8].

In this brief, we concentrate on the configuration and examination of WB-and SB-based CDMA encoding/interpreting technique, which relates to E, An, and D modules in Fig. 1.

#### B. CDMA Encoder

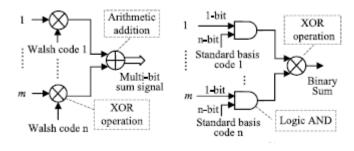

Two distinctive encoding techniques, WB encoder and SB encoder, are looked at in Fig. 2.

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

**ijates** ISSN 2348 - 7550

Fig. 2(a) demonstrates the WB encoder design. A unique information bit is initially encoded with a Walsh code by taking a XOR operation. At that point, these encoded information are signified a multibit aggregate sign by taking arithmetical increments. Every sender needs a XOR entryway, and different wires are utilized to express the aggregate sign in the event that we have two or more senders. In addition, the quantity of wires increments as the quantity of senders increments.

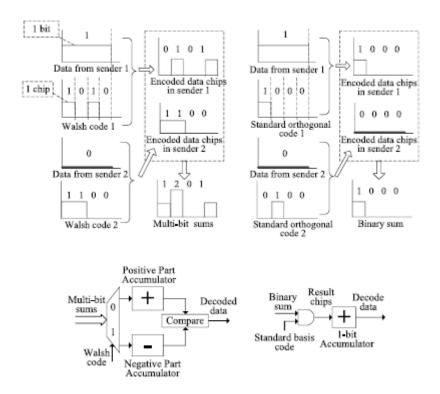

Fig. 2(b) demonstrates our SB encoding plan. A unique information bit from a sender is nourished into an AND entryway in a chip-by-chip way, what's more, it will be spread to n-chip encoded information with an orthogonal code of a standard premise. The relationship between a bit and a chip is appeared in Fig. 3. At that point, the encoded information from various senders are combined through a XOR operation, and a paired whole flag is produced. In this way, the yield sign is dependably a succession of paired sign exchanged to goal utilizing one single wire. The movements of both the encoding plans are delineated in Fig. 3. Fig. 3(a) and (b) represents the WB encoding process with four-chip Walsh codes and the SB encoding process with four-chip standard orthogonal codes, individually.

### C. CDMA Decoder

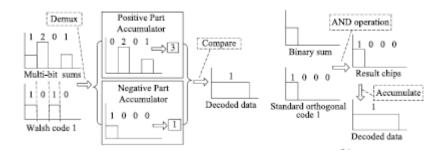

The WB deciphering plan is introduced in Fig. 4(a). Concurring to the chip estimation of Walsh code, the got multibit wholes are collected into positive part (if the chip worth is 0) or negative part (if the chip worth is 1). In this way, the two gatherers in the WB decoder independently contain a multibit viper to aggregate the coming chips and a gathering of registers to hold the amassed esteem. Through the correlation module after the two aggregators, the first information is remade. On the off chance that the estimation of positive part is vast, the first information is 1. Something else, the first information is 0.

Vol. No.4, Issue No. 09, September 2016 www.ijates.com

The SB translating plan is appeared in Fig. 4(b). At the point when the paired total sign touches base at collectors, an AND operation is taken between the parallel entirety and the relating orthogonal code in chip-bychip way. At that point, the outcome chips are sent to a gatherer. After m-chips are gathered (m is the length of the orthogonal code), the yield estimation of the gatherer will be the relating unique information. Note that there is constantly stand out chip equivalent to 1 and all other chips are equivalent to 0 for an orthogonal code in standard premise. Consequently, the maximal gathered worth in the SB collector is 1 and it can be put away in a 1-bit register. In this manner, in the SB interpreting module, one and only AND door and a gatherer with one 1-bit register are utilized, bringing about less sensible assets. A case of the unraveling procedure is represented in Fig. 5. In Fig. 5(a), at the WB decoder of collector 1, the aggregated worth 3 in the positive part is bigger than the amassed esteem 1 in the negative part. By the WB translating plan, the decoded information is 1, which is equivalent to the source information bit from sender 1. In Fig. 5(b), at the SB decoder of beneficiary 1, the yield estimation of the gatherer is 1, which is likewise equivalent to the source information bit from sender 1. Note that the translating brings about collector 2 are additionally right, however are not appeared in the figure. Subsequently, both strategies can recreate the first information bit from the entirety signal by utilizing their separate spreading codes

| Notations | Description                                                 |

|-----------|-------------------------------------------------------------|

| $I_j$     | the logical value of an original bit from sender $j$        |

| $I_j^i$   | the logical value of $i$ th chip in $I_j$                   |

| $C_j$     | the orthogonal code C allocated to sender j                 |

| $C_j^i$   | the logical value of $i$ th chip in $C_j$                   |

| $Y_j$     | the encoded data chips in sender j                          |

| $Y_j^i$   | the logical value of $i$ th chip in $Y_j$                   |

| S         | the sum of data chips generated by encoder                  |

| $S^i$     | the logical value of $i$ th chip in $S$                     |

| $M_j$     | data extracted from $S^i$ by AND gate in receiver $j$       |

| $M_j^i$   | the logical value of $i$ th chip in $M_j$                   |

| $O_j$     | the logical value of accumulator output bit in receiver $j$ |

| n         | the number of senders/receivers                             |

| m         | the number of chips in one bit                              |

We formally demonstrate the accuracy of our proposed SB plan. Documentations are characterized in Table I. As indicated by the SB plot, the encoded information Yj is produced by Ij and Cj with an AND

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

ijates ISSN 2348 - 7550

operation in a chip-by-chip way. Accordingly, the relationship of Yij, Iij, and Cij can be communicated by recipe (1) what's more, the estimation of the ith chip in the total information can be communicated by recipe (2)  $Yij = Iij \cdot Cij$  (1)

Si = Yi1  $\bigoplus$  Yi 2  $\bigoplus$  · · ·  $\bigoplus$  Yi n (2) where "·" (' $\bigoplus$ ') implies AND (XOR) operation.

In the decoder module, it first concentrates a succession of chips by AND operation and after that recreates the source information bit by collecting

Presently, we demonstrate that the first info bit Ij is equivalent to the yield bit Oj (without loss of all inclusive statement, we expect that the parcels from sender j are transmitted to collector j, and consequently the encoder j and the decoder j have the same orthogonal code Cj). From equations (1)–(4), we get We can streamline equation (5) by the accompanying strides.

- 1) According to the intelligent calculation properties, sensible conjunction can be conveyed over XOR.

- 2) In the standard premise, codes are orthogonal to each other and every code has one and stand out chip that is equivalent to 1.

- 3) For an orthogonal code in standard premise, every chip is a Boolean variable, and in this manner Cij  $\cdot$  Ci j is equivalent to Ci j agreeing to the impotency appropriateness for the consistent AND operation.

- 4) When a bit is separated into consecutive chips in the time space, the consistent estimation of that bit does not changed. In this manner, the intelligent estimation of chips is equivalent to each other, and it is moreover equivalent to that of the first piece. At the end of the day, we have  $I j = I1j = I2j = \cdot = Imj$ .

- 5) An orthogonal code in standard premise has one and one and only chip to be 1, and alternate chips are equivalent to 0. Subsequently, the aggregate of the considerable number of chips is equivalent to 1. From equation (5), we get that the sensible estimation of the decoder yield bit is constantly equivalent to the intelligent estimation of unique piece infused into the encoder. This demonstrates our proposed SB encoding/translating plan is right.

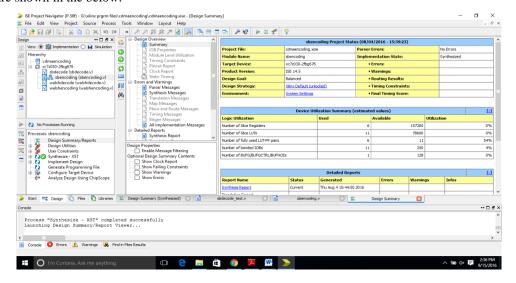

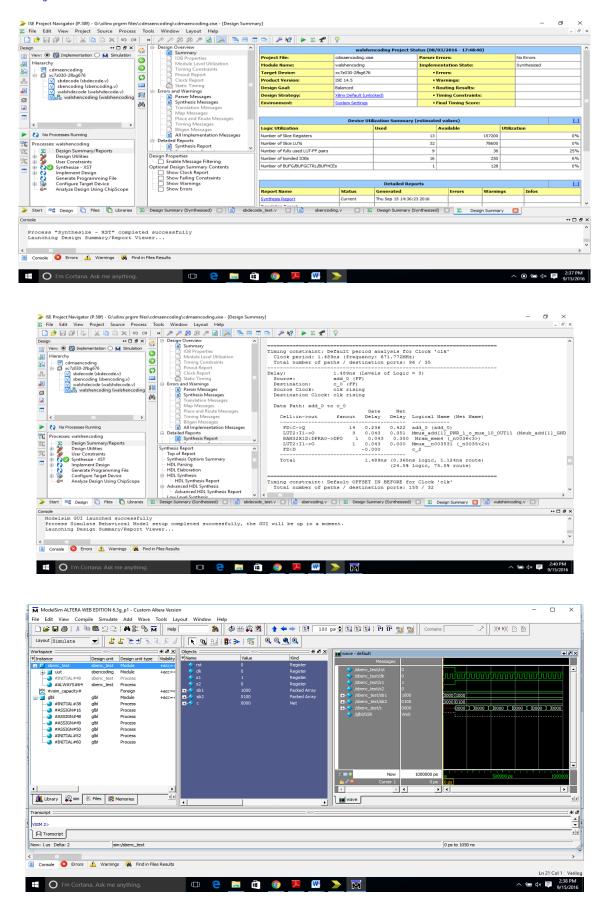

#### IV. SYNTHESIS AND SIMULATION RESULTS

This project was implemented with Verilog HDL using Xilinx ISE simulator, and synthesis and simulation results are shown in the below.

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

ijates ISSN 2348 - 7550

Vol. No.4, Issue No. 09, September 2016

www.ijates.com

**ijates**ISSN 2348 - 7550

#### IV. CONCLUSION

We propose another CDMA encoding/interpreting technique for on-chip correspondence. It can be acknowledged by utilizing straightforward rationale and expenses less power and region. The standard premise other than the Walsh code is utilized as the spreading code as a part of our strategy. It in this manner diminishes the encoding/interpreting inactivity and builds the most extreme throughput of NoCs. Numerical evidence is directed to demonstrate the rightness of our strategy. From the exploratory results, we find that our technique outflanks the WB encoding/deciphering plan, and the CDMA NoCexecution is additionally enhanced when our strategy is connected.

#### REFERENCES

- [1]. Jian Wang, Zhonghai Lu, and YubaiLiA New CDMA Encoding/Decoding Method foron-Chip Communication Network IEEE Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 24, No. 4, April 2016.

- [2] A. J. Viterbi, CDMA: Principles of Spread Spectrum Communication. Reading, MA, USA: Addison-Wesley, 1995.

- [3] S. Shimizu, T. Matsuoka, and K. Taniguchi, "Parallel bus systems using code-division multiple access technique," in Proc. Int. Symp. CircuitsSyst., May 2003, pp. II-240–II-243.

- [4] E. H. Dinan and B. Jabbari, "Spreading codes for direct sequence CDMA and wideband CDMA cellular

- [8] X. Wang, T. Ahonen, and J. Nurmi, "Applying CDMA technique to network-on-chip," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 10, pp. 1091–1100, Oct. 2007.

- [5] M. Kim, D. Kim, and G. E. Sobelman, "Adaptive scheduling for CDMA-based networks-on-chip," in Proc. 3rd Int. IEEE-NEWCASConf., Jun. 2005, pp. 357–360

- [6] A. Vidapalapati, V. Vijayakumaran, A. Ganguly, and A. Kwasinski, "NoC architectures with adaptive code division multiple access based wireless links," in Proc. IEEE Int. Symp. Circuits Syst., May 2012, pp. 636–639.

- [7] X. Wang and J. Nurmi, "Modeling a code-division multiple-access network-on-chip using SystemC," in Proc. Norchip, Nov. 2007, pp. 1–5

#### **AUTHOR DETAILS**

**MEDIKONDARAMAKRISHNA**, Pursuing M.techin Nalanda Institute of Engineering and Technology, He completed hisB.tech Electronics and Communication Engineering. His research of interest includes communication systems, Digital communications, Satellite communication etc.

**D.SUNEEL**, Working as assistant professors in Nalanda Institute of Engineering and Technology, He completed his Post Graduation, He has four years of teaching experience. Her research of interest includes communication systems, Digital communications, Satellite communication etc.