Vol. No.5, Issue No. 03, March 2017

www.ijates.com

# A BRIEF STUDY ON CHALLENGES OF MOSFET AND EVOLUTION OF FINFETS

J.Shailaja<sup>1</sup>, Y.Priya<sup>2</sup>

<sup>1</sup>ECE Department, Sphoorthy Engineering College (India) <sup>2</sup>ECE, Sphoorthy Engineering College, (India)

#### **ABSTRACT**

The present trend in engineering field is nano.Nano technology is found in all engineering and bio medical applications. All the analog and digital circuits of electronic fields are designed using transistors. The present scenario of chip designing is using nanolength channel transistors This paper has a study of nano scaling challenges of MOSFET, evolution of FinFET.

Keywords: Challenges of MOSFETs, FinFETs

#### **I INTRODUCTION**

The rapid progress of silicon technology is continuing with present generation technologies of gate lengths less than 22 nm. Moore's law states the scaling of ICs, which carried out a lot of research in Nano world. Early years of silicon era used MOSFETs for designing the circuits. Many research articles have been published that demonstrate the improved short-channel effects of conventional bulk MOSFETs [1-4,5-7]. FinFET and Trigate devices have been explored thoroughly in the past decade [8–15]. Power Challenges introduced by nanometre gate length are Short Channel effects and Variability. Section II introduces the Short channel effects(SCE) [18]. Change of Materials to over come SCE is discussed in Section IVI [16]. FinFETs are studied in section V[16,18].

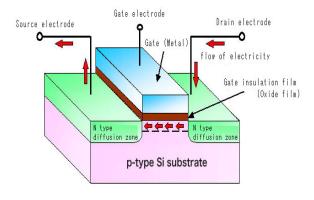

Construction of MOSFET

**Figure: 1 Structure of MOSFET**

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

ISSN 2348 - 7550

II SHORT CHANNEL EFFECTS

For MOSFET gate length less than 10nm, the mechanical tunnelling from source to drain becomes significant. Tunnelling degrades the sub threshold slope and increases the leakage current in OFF State [17].Different Physical Phenomena contribute to Short channel effects. The OFF- current of Short channel Transistors is

influenced by Threshold voltage, Channel Physical dimensions, Channel doping, Drain/Source Junction depths,

gate oxide thickness, The supply voltage, Drain and Gate Voltages.

Different Short channel leakage currents are Weak Inversion, Drain Induced Barrier-Lowering Effect, Gate

Induced Drain Leakage and Punch through.

III CHANGE OF MATERIALS

To increase the power and speed of the circuits, the size of the transistors are shrinked. To Shrink the device,

gate length is reduced (W/L ratio ),if Channel length reduces, Oxide thickness must be reduced. If Oxide

thickness gets small (nm),device leaks. But Oxide thickness must shrink with the device. This effects the control

of gate over the channel. Two choices to overcome the effect of Dennard'scaling[20].

a) Change Materials of transistor: To reduce the size ,thickness of oxide layer must be reduced but capacitance

across oxide must be constant.

$C_{ox} = \epsilon_{ox} K A/T_{ox}$  [20]

K- Dielectric constant, A- Area

Cox-Oxide Capacitance, Tox-Oxide Thickness

Dielectric constant must be increased to maintain constant oxide capacitance as shown in the equation.

Therefore change of material from silicon dioxide layer to Hfo<sub>2</sub>. Dielectric constant of Hfo<sub>2</sub> increases by four

times than Silicon oxide layer.

IV CHANGE GEOMETRY OF TRANSISTOR

To Overcome SCE and Variability new technologies in geometry of transistors were introduced [16]. Such as

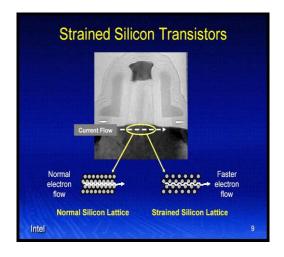

a) Strained Silicon: Thin silicon layer is deposited over the silicon germanium substrate. As silicon atoms align

with silicon germanium substrate, the links between silicon atoms are stretched or compressed which leads to

strained silicon. This reduces the atomic forces, which inturn increases the mobility of electron. Higher mobility

increases performance of the device .Shown in Figure 1

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Figure: 2 Strained Silicon Transistors

- b) Hetero Junction devices: Hetero structures developed by Stanford has larger carrier mobility but requires larger time.

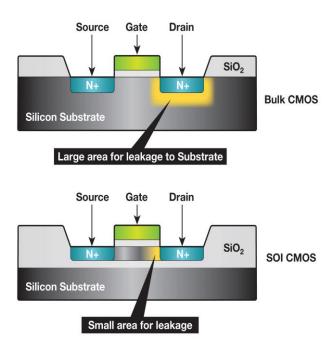

- c) Silicon on Insulator: The channel is formed in a thin layer of silicon deposited above an electrical insulator. This structure reduces junction capacitance which inturn reduces power. Other advantages are higher subthreshold slope factor, reducing leakage, reduced impact of soft errors, but more expensive and has secondary effects. Silicon on insulator are classified as FD-SOI( fully depleted silicon on insulator), PD-SOI(partially depleted silicon on insulator). Shown in Figure 2

Figure: 3 Structure of CMOS and SOI-CMOS

Vol. No.5, Issue No. 03, March 2017 www.ijates.com

#### V FinFET

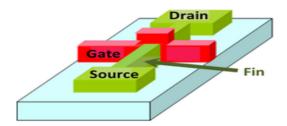

FinFETs are replacing Bulk CMOS devices at NanoScale. The term FinFET was given by researchers at university of California at Berkely. Unlike MOSFET the gate is wrapped around a thin Silicon Fin which forms the body of the device. Channel length determines the dimensions of FinFET. The device structure shows the potential to scale the channel length to values that are impossible to accomplish in traditional planar devices. Operational transistors with channel lengths of 7nm had been demonstrated [16].

Structure of FinFET consists of a thin vertical Fin on a substrate which runs between source and drain. Gate is wrapped around the Fin structure in traverse form. Electrical control over the channel conduction is improved by this type of gate structure, as well overcomes the short channel effects. The term FinFET is ued generically to describe any Fin-Based, Multi-gate Transistors.

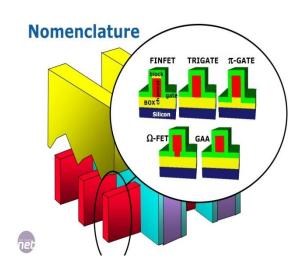

Depending on the structure of FinFET, different types of FinFETs are available such as double gateFinFET, Multi gate FinFET, Trigate FinFET, Omega –FinFET, All Around Gate FinFET(AAG).Both FullyDepleted SOI and DGFinFET have similar advantages, but DG-FinFET has relaxed constriant of channel thickness.Therefore FinFETs are more Scalable thanFD-SOI.Among all multigate FETs, Double gate and Trigate FinFETs aremost popular for their simple structure and ease of fabrication.Two or three gates wrapped arounda vertical channel enable easy alignment of gates.[18]

Figure: 4 Structure of FinFET

Figure: 5 Different Structures of FinFET

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

#### VI CONCLUSION

This paper has a study of Nano scaling Challenges of MOSFETS, which are nothing but short channel effects and variability. To overcome this, different structures have been discussed. Finally FinFETs have been studied.

#### **REFERENCES**

- 1. D. Hisamoto, W.-C. Lee, J. Kedzierski et al., "FinFET—a self-aligned double-gate MOSFET scalable to 20 nm," IEEE Transactions on Electron Devices, vol. 47, no. 12, pp. 2320–2325, 2000.

- 2. B. Yu, L. Chang, S. Ahmed et al., "FinFET scaling to 10 nm gate length," in Proceedings of the IEEE International Devices Meeting (IEDM '02), pp. 251–254, San Francisco, Calif, USA, December 2002.

- 3. S. Tang, L. Chang, N. Lindert et al., "FinFET—a quasiplanar double-gate MOSFET," in Proceedings of the International of Solid-State Circuits Conference, pp. 118–119, February 2001.

- 4. M. Guillorn, J. Chang, A. Bryant et al., "FinFET performance advantage at 22 nm: an AC perspective," in Proceedings of the Symposium on VLSI Technology Digest of Technical Papers (VLSIT '08), pp. 12–13, June 2008.

- 5. J. Gu, J. Keane, S. Sapatnekar, and C. H. Kim, "Statistical leakage estimation of double gate FinFET devices considering the width quantization property," IEEE Transactions on Very Large Scale Integration Systems, vol. 16, no. 2, pp. 206–209, 2008.

- 6. D. Ha, H. Takeuchi, Y.-K. Choi, and T.-J. King, "Molybdenum gate technology for ultrathin-body MOSFETs and FinFETs," IEEE Transactions on Electron Devices, vol. 51, no. 12, pp. 1989–1996, 2004.

- 7. T. Sairam, W. Zhao, and Y. Cao, "Optimizing FinFET technology for high-speed and low-power design," in Proceedings of the 17th Great Lakes Symposium on VLSI (GLSVLSI '07), pp. 73–77, March 2007.

- 8. A. N. Bhoj and N. K. Jha, "Design of logic gates and flip-flops in high-performance FinFET technology," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 11, pp. 1975–1988, 2013.

- 9. S. A. Tawfik and V. Kursun, "Characterization of new static independent-gate-biased FinFET latches and flip-flops under process variations," in Proceedings of the 9th International Symposium on Quality Electronic Design (ISQED '08), pp. 311–316, San Jose, Calif, USA, March 2008.

- 10. S. A. Tawfik and V. Kursun, "Low-power and compact sequential circuits with independent-gate FinFETs," IEEE Transactions on Electron Devices, vol. 55, no. 1, pp. 60–70, 2008.

- A. Bansal, S. Mukhopadhyay, and K. Roy, "Device-optimization technique for robust and low-power FinFET SRAM design in NanoScale era," IEEE Transactions on Electron Devices, vol. 54, no. 6, pp. 1409– 1419, 2007.

- 12. A. N. Bhoj and R. V. Joshi, "Transport-analysis-based 3-D TCAD capacitance extraction for sub-32-nm SRAM structures," IEEE Electron Device Letters, vol. 33, no. 2, pp. 158–160, 2012.

Vol. No.5, Issue No. 03, March 2017

### www.ijates.com

ISSN 2348 - 7550

- 13. A. N. Bhoj, R. V. Joshi, and N. K. Jha, "Efficient methodologies for 3-D TCAD modeling of emerging devices and circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 32, no. 1, pp. 47–58, 2013.

- 14. A. N. Bhoj and N. K. Jha, "Parasitics-aware design of symmetric and asymmetric gate-workfunction FinFET SRAMs," IEEE Transactions on Very Large Scale Integration Systems, vol. 22, no. 3, pp. 548–561, 2014.

- 15. K. Endo, S.-I. O'Uchi, T. Matsukawa, Y. Liu, and M. Masahara, "Independent double-gate FinFET SRAM technology," in Proceedings of the 4th IEEE International Nanoelectronics Conference (INEC '11), pp. 1–2, June 2011.

- 16. Ali Javey and Jing Kong," Carbon Nanotube Electronics", ISBN 978-0-387-71712-8.

- 17. Jing Wang and Mark Lund Storm, "Microelectronics, Nanoelectronics, and the Future of electronics".

- DebajitBhattacharya and Niraj k Jha"FinFETs:FromDevicestoArchitecture" Advance in Electronics,

Volume 2014 (2014), Article ID 365689Department of Electrical Engineering, Princeton University,

Princeton, NJ 08544, USA

#### **Reference Books**

19. Low-Power VLSI Circuit Design by Kaushik Roy, Sharat C. Prasad, Wiley Publications,

Videos:

20.https://www.youtube.com/watch?v=V1HN0w\_aJgg&t=470s