Vol. No.5, Issue No. 03, March 2017

www.ijates.com

# SINGLE PHASE HYBRIDIZED NINE-LEVEL INVERTER

## K.Sudharshan<sup>1</sup>, Bhanutej Jawabu Naveez<sup>2</sup>

<sup>1</sup>Associate professor, Dept of EEE, Khader Memorial College of Engineering & Technology, JNTUH, TS (India)

<sup>2</sup>Assistant Professor, Dept of EEE, VBIT, Hyderabad, JNTUH, TS (India)

#### **ABSTRACT**

The main objective of this paper is to analyze two different types of nine level inverters. This paper depends on the multilevel converters with multiple numbers of DC sources and presents cascaded H-bridge nine level inverter and multi string nine level inverter topologies with four input DC sources. The purpose of this paper is to show the differences between these two converters in terms of modulation scheme, switching losses. These comparisons were never made between cascaded H-bridge multi-level converter (CHBMC) and multi string multi-level inverter (MMC). The modulation schemes and the determination of unipolar PWM modulation signals of these two converters are discussed. The switching losses between these two converters are also discussed. Simulation and experimental results of the two converters validate the proposed analysis.

Keywords: Multilevel inverter, LS - PWM, modulation index.

#### I. INTRODUCTION

In the last few years, the necessity of increasing the power level in the industry has sustained the continuous development of multilevel converters due to their capability of handling voltages up to 6.9kv and power of several megawatts. Since the presentation of multilevel cascade H-bridge (CHBMC) in

1975 [2], the converter has received much research attention due to their several advantages compared to other multilevel converter topologies in terms of simplicity, modularity, reliability and the number of levels with a minimum number of power semiconductor devices Environmental friendly distributed energy resources (DERs) are very well desired in the light of global warming and climate change. The integrating interface converters of DERs are used for photovoltaic panels (PV), wind power, micro turbines and fuel cells. These converters deliver electric power in terms of high efficiency and reliability. Multi-level inverters are generally used as an interface between the photovoltaic panels and the utility grid. So there is a need to find the effective converter that can be used as an interface. When compared with the present available multi-level converters, the both cascaded H-bridge (CHBMC) and multi string multi-level inverters (MMC) would be better and efficient interfaces.

The CHBMC has been employed to develop different applications, such as synchronous rectifiers, inverters, STATCOM, active filters, renewable energy integration systems, motor drives, etc. Moreover, specific control strategies and modulation techniques, associated with those applications, have been designed for this converter configuration. The behavior of the CHBMC during transient and steady-state operations can be estimated from

Vol. No.5, Issue No. 03, March 2017

#### www.ijates.com

ijates ISSN 2348 - 7550

the model of the inverter. Multi-level cascaded H-bridge single phase DC-AC converter with reduced voltage ripple can be an advantageous utility as an interface between the photovoltaic panels and the utility grid.

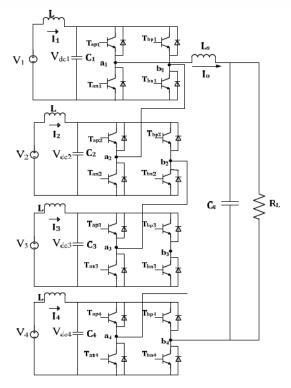

## II. TOPOLOGIES OF CASCADED H-BRIDGE AND MULTI STRING NINE-LEVEL INVERTERS CHBMC

A multilevel cascaded inverter consisting of four H bridges is shown in Fig. 1. The individual output voltages of the each cells are Vabi, and Tapi, Tbpi and Tani, Tbni are the switching functions of the upper and lower switches, respectively (where i=1, 2, 3 and 4). The equations for the output voltages of individual cells in terms of input DC voltages are given as follows.

$$\begin{split} V_{ab1} &= V_{dc1} \left( S_{ap1} - S_{bp1} \right), \\ V_{ab2} &= V_{dc2} \left( S_{ap2} - S_{bp2} \right) \\ V_{ab3} &= V_{dc3} \left( S_{ap3} - S_{bp3} \right), \\ V_{ab4} &= V_{dc4} \left( S_{ap4} - S_{bp4} \right) \end{split} \tag{1}$$

Therefore VAB = Vab1 + Vab2 + Vab3 + Vab4

$$V_{AB} = \begin{bmatrix} V_{dc1} \left( S_{ap1} - S_{bp1} \right) + V_{dc2} \left( S_{ap2} - S_{bp2} \right) \\ + V_{dc3} \left( S_{ap3} - S_{bp3} \right) + V_{dc4} \left( S_{ap4} - S_{bp4} \right) \end{bmatrix} \tag{2}$$

The equations for the input currents are also given by

$$\begin{split} I_{s1} &= I_{o1} \left( S_{ap1} - S_{bp1} \right), \\ I_{s2} &= I_{o2} \left( S_{ap2} - S_{bp2} \right) \\ I_{s3} &= I_{o3} \left( S_{ap3} - S_{bp3} \right), \\ I_{s4} &= I_{o4} \left( S_{ap4} - S_{bp4} \right) \end{split} \tag{3}$$

Where Io1, Io2, Io3, Io4 are the individual output currents from beach inverter cell. Io1 = Io2 = I o3 = I o4 when the cells are connected in cascade.

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

**ijates** ISSN 2348 - 7550

Fig.1. Four level cascaded H-bridge converter

## **III.MODULATION PROCESS**

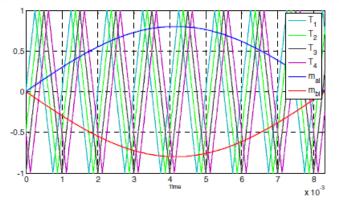

## **CHBMC (Phase Shifted PWM):**

Consider an 'n' level converter, then the total number of switches in 'n' level converter are 2(n-1). For generating the carrier based PWM, minimum two modulation signals and (n-1)/2 carrier waveforms are required. The modulation strategy developed in this work is a phase shifted unipolar pulse width modulation scheme. The two legs of the full-bridge inverter are controlled separately by comparing a high frequency triangular carrier with two line frequency modulating signals which are displaced by  $180^{\circ}$  out of phase from each other. As shown in Fig. 2, mai, mbi are the modulation signals for each leg of the single inverter. T1,T2,T3 and T4 are the triangle carrier signals corresponding to each H-bridges and they all are displaced by 45 from each other. Each switching pulses are generated as follows

```

S_{api} = 1 if m_{ai} > T_i and 0 otherwise S_{bpi} = 1 if m_{bi} > T_i and 0 otherwise S_{ani} = 1 if m_{ai} < T_i and 0 otherwise S_{bni} = 1 if m_{bi} < T_i and 0 otherwise Where i=1, 2, 3 and 4

```

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Fig. 2. Modulation Scheme of CHBMC

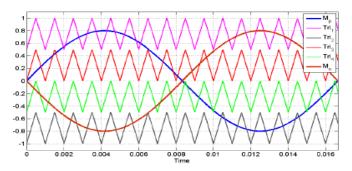

## **MULTI STRING MC (Level Shifted PWM):**

Fig. 3. Modulation Scheme of multi string mc

For modulation scheme, level shifted carrier based PWM is used. In level shifted PWM, the carrier waveforms are one above another with equal amplitude. If the switching pulses of switches in one leg are generated, then their complementary will be respectively the switching pulses of switches in another leg. The generation of switching pulses ifollows:

$$\begin{split} S_{ap} &= \begin{bmatrix} 1 \text{ when } \begin{pmatrix} Tri_1 < M_p < Tri_2 \text{ for } M_p > 0, \\ M_p > Tri_3, M_p < Tri_4 \text{ for } M_p < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} M_p > Tri_1, M_p < Tri_2 \text{ for } M_p > 0, \\ Tri_3 < M_p < Tri_4 \text{ for } M_p < 0 \end{pmatrix} \\ S_{am} &= \begin{bmatrix} 1 \text{ when } M_p > Tri_2 \text{ for } M_p > 0 \text{ and } M_p > Tri_3 \text{ for } M_p < 0 \\ 0 \text{ when } M_p < Tri_2 \text{ for } M_p > 0 \text{ and } M_p < Tri_3 \text{ for } M_p < 0 \end{bmatrix} \\ S_{an} &= \begin{bmatrix} 1 \text{ when } M_n > 0 \\ 0 \text{ when } M_n < 0 \end{bmatrix} \\ 0 \text{ when } M_n < 0 \\ 0 \text{ when } M_n < 0 \end{bmatrix} \\ S_{ao} &= \begin{bmatrix} 1 \text{ when } M_n < Tri_2 \text{ for } M_n > 0 \text{ and } M_n < Tri_3 \text{ for } M_n < 0 \\ 0 \text{ when } M_n > Tri_2 \text{ for } M_n > 0 \text{ and } M_n > Tri_3 \text{ for } M_n < 0 \end{bmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_3 < M_n < Tri_4 \text{ for } M_n < 0, \\ M_n < Tri_2, M_n > Tri_1 \text{ for } M_n > 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n > 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n < 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n < 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n < 0, \\ M_n > Tri_3, M_n < Tri_4 \text{ for } M_n < 0 \end{pmatrix} \\ 0 \text{ when } \begin{pmatrix} Tri_1 < M_n < Tri_2 \text{ for } M_n < 0, \\ M_n < Tri_2 \text{ for } M_n < 0, \\ M_n < Tri_2 \text{ for } M_n < 0, \\ M_n < Tri_2 \text{ for } M_n < 0, \\ M_n < Tri_2 \text{ for } M_n$$

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

**ijates** ISSN 2348 - 7550

Where M p and Mn are the modulation signals and Tri1, Tri2, Tri3 and Tri4 are the four carrier waveforms used to generate switching pulses by level shifted carrier based PWM. The modulation signals and carrier waveforms can be seen in Fig. 3.

#### IV. SIMULATION RESULTS

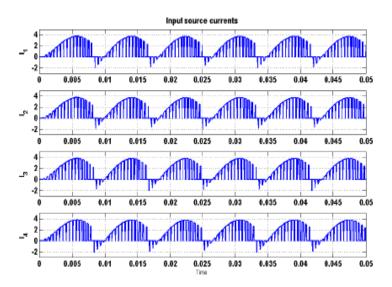

#### **CHBMC:**

Fig 4: Input current source

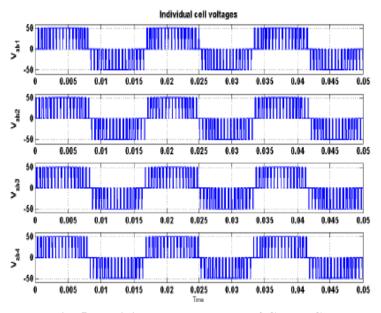

Fig. 5. Individual cell voltages of CHBMC

The proposed modulation scheme is implemented on four cell cascaded H-Bridge Multi level converter. Simulation Results are done on Four cell cascaded H-Bridge Single phase AC-Dc converter is used to generate AC voltage when each of four cell is fed with 50v dc.

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

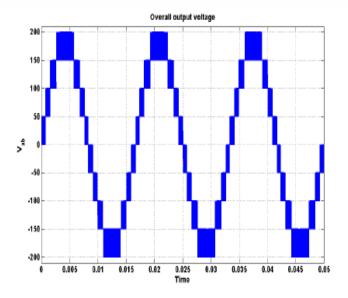

Fig. 6. Overall output voltage of CHBMC

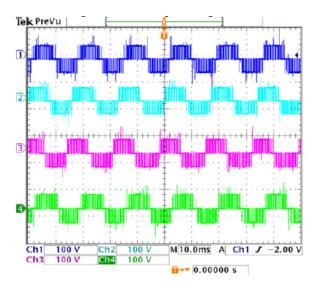

Fig. 7. Experimental waveform of Individual cell voltages of CHBMC

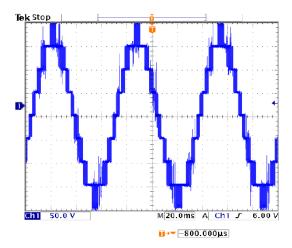

Fig. 9. Experimental waveform of overall output voltage of CHBMC

Fig. 5, and Fig. 6 shows the simulation results of individual output voltage of each cell and the overall output voltage of the inverter based on the proposed method.

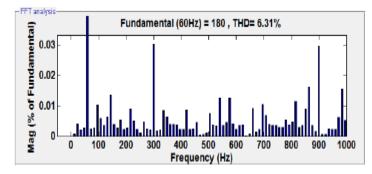

Fig. 7, and Fig. 8 validate the simulation results of individual output voltage of each cell and the overall output voltage of the inverter. The Fourier spectrum analysis of the overall output voltage is seen in Fig. 9. As we can

Vol. No.5, Issue No. 03, March 2017

#### www.ijates.com

1jates

see from this Fourier spectrum that the harmonic magnitude of the 3rd, 5th. 7th and9th harmonics is less than 0.05% of fundamental voltage. Therefore, this result verifies that the modulation indices calculated based on the proposed technique results in the minimization of harmonics.

Fig. 10. Experimental waveform of Output voltage of multi string ninelevel converter

#### IV CONCLUSION

This paper presents two single-phase DC-AC multi-level converters which utilizes same number of DC sources. The topologies of both the inverters are presented and compared. The phase shift carrier based PWM for CHBMC and level shift carrier based PWM for multi string multi-level converters are also presented. The unipolar PWM modulation signals using double Fourier series for CHBMC and double Fourier series approximation of switching functions for multi string multi-level converter are determined. The switching losses between two converters are approximated and are also compared. Simulation and experimental results of both the converters are carried out and they validate each other and also the proposed analysis. The only disadvantage with this type of converter when compared with cascade H bridge multi-level converter is rating of middle switches which should be twice of other four switches.

## **REFERENCES**

- [1] S. Alepuz, S. Busquets-Monge, J. Bordonau, J. Gago, D. Gonzalez and J. Balcells, "Interfacing renewable energy sources to the utility grid using three-level inverter," *IEEE Transaction on Industrial Electronics*, vol. 53, no. 5, pp. 1504 1511, Oct. 2006.

- [2] S. Vazquez, J. I. Leon, Leopoldo G. Franquelo, Jose J. Padilla, and Juan M. Carrasco, "DC-Voltage-Ratio Control Strategy for Multilevel Cascaded Converters Fed With a Single DC Source," *IEEE Transaction on Industrial Electronics*, vol. 56, no. 7, pp. 2513-2521, Jul. 2009.

- [3] J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls and applications," *IEEE Transaction on Industrial Electronics*, vol. 49, no. 4, pp. 724 728, Aug. 2002.

- [4] C. L. Chen, Y. Wang, J. S. Lai, Y. S. Lee, and D. Martin, "Design of parallel inverters for smooth mode transfer micro grid applications," *IEEE Transactions on Power Electronics*, vol. 25, no. 1, pp. 6–15, Jan. 2010.

Vol. No.5, Issue No. 03, March 2017

## www.ijates.com

ijates ISSN 2348 - 7550

- [5] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformerless single-phase multilevel-based photovoltaic inverter," *IEEE Trans. Industrial Electronics*, vol. 55, no. 7, pp. 2694-2702, Jul. 2008.

- [6] J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls and applications," *IEEE Transaction on Industrial Electronics*, vol. 49, no. 4, pp. 724 728, Aug. 2002.

- [7] D. G. Holmes and T. A. Lipo, Pulse width modulation for power converters, New York: Wiley, 2003.

- [8] H. Iman-Eini, J. L. Schanen, S. Farhangi and J. Roudet, "A modular strategy for control and voltage balancing of cascade H-bridge rectifiers," *IEEE Transaction on Industrial Electronics*, vol. 23, no. 5, pp. 2428 2442, Sep. 2008.

- [9] P. Lezana, J. Rodriguez and J.A. Oyarzun, "Cascaded multilevel inverter with regeneration capability and reduced number of switches," *IEEE Transaction on Industrial Electronics*, vol. 55, no. 3, pp. 1059 1066, Mar. 2008

#### **Author's Profile:**

Sudharshan Kotha is working as an Associate professor in KHADER Memorial College of Engineering & Technology, He has completed M.Tech from JNTUH Campus,he has 8 years of teaching experience,his intrest of areas in research is power electronics and its applications.

Bhanutej Jawabu naveez is working as an Assistant professor in VBIT, Hyderabad, He has completed his B.Tech, M.Tech from JNTUH, Currently pursuing PhD at VIT University Vellore, he has 5 years of teaching experience, his research are power electronics converters, multilevel inverters for grid connected PV applications.