Vol. No.5, Issue No. 03, March 2017

www.ijates.com

# CLOSED LOOP OPERATION OF DC-AC DUAL BUCK FULL BRIDGE INVERTER FOR GRID CONNECTED OPERATION OF RENEWABLE ENERGY SOURCES

S.Mageshwari<sup>1</sup>, M.Nipuan<sup>2</sup>, S.KanagaLakshmi<sup>3</sup>

<sup>1,2</sup>EEE Department, National Institute of Technology, Tiruchirappalli, (India)

<sup>3</sup>Instrumentation Engineering Department, Madras Institute of Technology, Chennai, (India)

#### **ABSTRACT**

Renewable energy and distributed generation are getting more and more popular, including photovoltaic modules (PV), wind turbines, and fuel cells. The renewable energy sources need power electronics circuits to interface with the utility grid because of different characteristics between the sources and the grid. No matter what renewable energy source is utilized, inverters are essential in the micro grid system. In this work, a Dual-Buck Full-Bridge Inverter (DBFBI) is used to solve the shoot-through problem in conventional bridge-type inverters and reduce the voltage stress of the power device in the Dual-Buck Half-Bridge Inverter (DBHBI). Hysteresis current control is used in the DBFBI. All switches and diodes operate at each half line cycle, and the freewheeling current flows through the independent freewheeling diodes instead of the body diodes of the switches, so the efficiency can be increased potentially. As the shoot-through problem does not exist in the DBFBI, dead time between the switches need not be set. The input voltage utilization rate of the DBFBI is twice that of the DBHBI under the same output-voltage condition, i.e., the voltage stress of the power device in DBFBI is half that in the DBHBI. The operating principle and design guidelines are provided. The simulation of the DBFBI has been done in PSCAD and the performance of the inverter during dc input voltage variations, reference voltage variation, with nonlinear load and with grid interconnection with active and reactive power control has been analyzed.

Keywords: Full- Bridge, Half-Bridge, Hysteresis Current Control, Inverter, Micro Grid System, Renewable Energy.

#### I INTRODUCTION

Various studies on inverter have been reported in literature so far. The inverter plays an important role in distributed generation systems [1]. Fossil fuel reserve availability and environmental concerns are now the driving forces behind the use of new clean and renewable energy sources, such as photovoltaic energy, wind energy, and fuel cell, which are the input sources of distributed generation systems.

Among various multilevel voltage-source inverters, the most commonly used and commercially available ones are the neutral-point-clamped inverter, flying capacitor inverter and cascade H-bridge inverter [2]-[5]

Vol. No.5, Issue No. 03, March 2017

### www.ijates.com

1Jales 1991 2348 - 7550

Cascade inverters are with separate dc sources, and each dc source is associated with a single-phase inverter while the ac terminals of each inverter are connected in series. It was first invented by Richard H. Baker back in 1975 [6].

However, because most of current cascade inverters are based on a series connection of several single voltage source inverters with two active devices in one leg, a shoot-through problem exists in a conventional bridge-type voltage-source inverter [7], which is a major killer of the reliability of the inverter. Dead time to block the upper and lower devices of each phase leg has to be provided in the voltage-source inverter.

A dual-buck half-bridge inverter [8], has been proposed to solve the shoot-through problem. However, the input-voltage utilization rate of the DBHBI is just half that of the full-bridge inverter and the voltage stresses on the switches will be high. Another problem faced is that in inverter's voltage dividing capacitors are present and capacitor voltage balance issues will be there [9]. If the voltage is not balanced, then even harmonics will be produced in the output.

In order to solve the aforementioned problems, a dual-buck full-bridge inverter with hysteresis current control is proposed and analysed stability and relative stability [10]. The shoot-through problem does not exist in the DBFBI. The DBFBI has the same input voltage utilization rate as the full-bridge inverter, and thus, the voltage stress of the power device in the DBFBI is half that in the DBHBI. The freewheeling current flows through the independent freewheeling diodes instead of the body diodes of the switches, so the freewheeling diodes can be designed optimally.

The DBFBI topology and operating principle is described in Section 2. The design guidelines are presented in Section 3. The Grid connected operation of DBFBI is presented in Section 4. In Section 5, the simulation results from a DBFBI which confirm the theoretical analysis is presented. Finally, concluding remarks are given in Section 6.

#### II DBFBI TOPOLOGY AND OPERATING PRINCIPLE

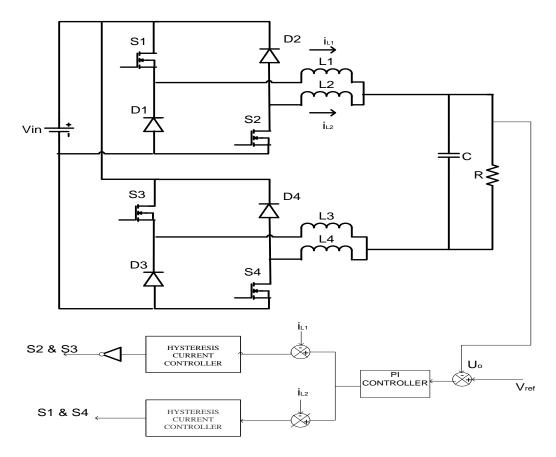

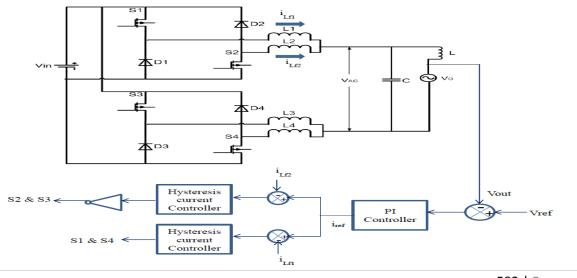

The topology of DC-AC dual buck full bridge inverter is presented in this section. The operation of the inverter is described with the help of a block diagram and circuit diagram in Fig.1. Closed loop study of DBFBI using hysteresis current control is explained.

To commence with the analysis, assumptions are made as follows.

- All the switches and diodes are ideal.

- All the inductors and capacitors are ideal.

- The input voltage  $(V_{in})$  is larger than the maximum output voltage  $(U_0)$ .

- $L_1 = L_2 = L_3 = L_4 = L$

- Filter inductor currents  $i_{L1} = i_{L4}$  and  $i_{L2} = i_{L2}$ , where  $V_{ref}$  is the reference voltage, and  $U_o$  is the output feedback voltage.

The circuit operation is explained in terms of two modes (for positive half cycle), the switch S1 and S4 are controlled to operate synchronously to get positive half cycle output:

Vol. No.5, Issue No. 03, March 2017

### www.ijates.com

ISSN 2348 - 7550

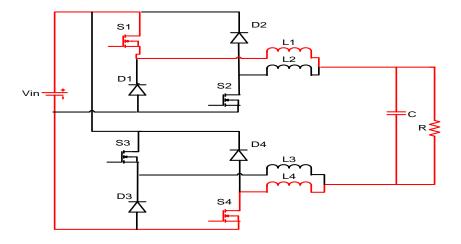

- During mode 1 (Fig. 2), the switches S1 and S4 are ON (SPWM pulses), the inductor current  $L_1$  and  $L_4$  rises.

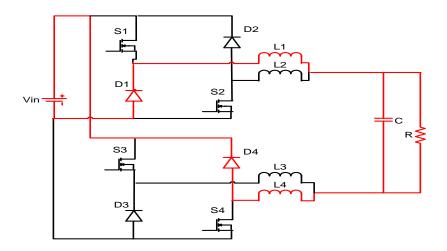

- In mode 2 (Fig. 3), the switches S1 and S4 are OFF, the inductor current  $L_1$  and  $L_4$  will freewheels through D1 and D4.

- Similarly, for getting negative half cycle, switches S2 and S3 will be controlled synchronously (SPWM pulses). There also 2 modes of operation are available, same as the above.

Fig. 1. DBFBI based Hysteresis current control

Table. 1. Switching Pattern for Mode 1

| Switch/diode | S1 | S2  | S3  | S4 | D1  | D2  | D3  | D4  |

|--------------|----|-----|-----|----|-----|-----|-----|-----|

| Mode 1       | ON | OFF | OFF | ON | OFF | OFF | OFF | OFF |

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Fig. 2. DBFBI in Mode 1 for Positive Half Cycle

Fig. 3. DBFBI in Mode 2 for Positive Half Cycle

Table. 2. Switching Pattern for Mode 2

| Switch/diode | S1  | S2  | S3  | S4  | D1 | D2  | D3  | D4 |

|--------------|-----|-----|-----|-----|----|-----|-----|----|

| Mode 2       | OFF | OFF | OFF | OFF | ON | OFF | OFF | ON |

There are two switching modes at each half line cycle

### 1. Reference current $i_{ref} > 0$

As can be seen from the Fig. 2 and Fig. 3 S1 and S4 are controlled to operate synchronously. S2 and S3 are always turned off at this half line cycle, and thus,  $i_{L2}$  and  $i_{L3}$  are equal to zero.

### • MODE 1 $[i_{L1} < i_{ref} - h/2]$

In Fig. 2. S1 and S4 are gated on. The voltages across D1 and D4 are equal to  $V_{in}$ . The current  $i_{L1}$  and  $i_{L4}$  increase linearly. In this mode,

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

$$2L\frac{d}{dt}i_{L1} = V_{in} - U_o \tag{1}$$

Where  $U_o$  is the instantaneous output voltage.

### MODE 2 [ $i_{L1} > i_{ref} + h/2$ ]

In Fig. 3. S1 and S4 are gated off, and D1 and D4 are forward biased, so the voltage across the switches equal to  $V_{in}$ . The current  $i_{L1}$  and  $i_{L4}$  decay linearly. In this mode,

$$2L\frac{d}{dt}i_{L1} = -V_{in} - U_o \tag{2}$$

The relationship of  $U_0$  with  $V_{in}$  can be obtained by using (1) and (2)

#### 2. Reference current $i_{ref} < 0$

The operating principle at this half line cycle is similar to that at  $i_{ref} > 0$ .

#### III DESIGN GUIDELINES

#### A. Selecting the Input Voltage

The voltage  $V_{in}$  must be larger than the maximum output voltage.

#### B. Switching Frequency range

According to the hysteresis band and the wave shape of inductor current, switching frequency varies.

The instantaneous switching frequency can be deduced from (1) and (2)

$$f_{\rm S} = \frac{V_{\rm in}^2 - U_{\rm o}^2}{4Lh\,V_{\rm in}}\tag{3}$$

the maximum and minimum switching frequencies happen at  $U_o = 0$  and  $U_o = \sqrt{2}V_o$ , respectively, which are given by

Maximum switching frequency,

$$f_{s \text{ max}} = \frac{V_{in}}{4Lh}$$

(4)

Minimum switching frequency,

$$f_{s \min} = \frac{v_{in}^2 - 2U_o^2}{4Lh V_{in}}$$

(5)

Where  $U_o$  is the root mean square (rms) of the output voltage.

The average switching frequency can be obtained as

$$f_{\text{s avg}} = \frac{V_{\text{in}}^2 - U_0^2}{4Lh V_{\text{in}}} \tag{6}$$

The maximum switching frequency  $f_{s \text{ max}}$  cannot be too large; otherwise, a large switching loss may break the switches.

#### C. Hysteresis-band selection

As can be seen from (4), when  $V_{in}$  and  $f_{s max}$  are fixed on, h cannot be too small; if not, the filter inductor value will be large. It cannot also be too large, or else, the ripple current will be large, and thus, the losses of the switches, diodes, and filter inductors will be high, and the tracking accuracy will be reduced with  $i_{ref}$ .

In this way, h is chosen to be 50% of the rated load current, i.e.,

$$h = \frac{0.5 \, S_{\odot}}{U_{\odot}} \tag{7}$$

Vol. No.5, Issue No. 03, March 2017

#### www.ijates.com

**ijates** ISSN 2348 - 7550

Where  $S_o$  is the apparent power of the inverter.

#### D. Filter Inductor Design

When  $V_{in}$ ,  $f_{s max}$ , and h are fixed on, the filter inductance can be calculated as

$$L = \frac{v_{in}}{4hf_{s max}} \tag{8}$$

#### E. Filter Capacitor Design

The filter capacitor is designed by the corner frequency of the LC filter, which should be larger by 10–20 times of  $f_0$  (output frequency) and lower by 1/20-1/10 of  $f_{\rm s\,avg}$ . The filter capacitance can be calculated as

$$C_f = \frac{1}{2(2\pi f)^2 L} \tag{9}$$

**Table. 3. Parameters and Design Values**

| Parameters    | Vi   | $\mathbf{U_0}$ | $\mathbf{f_0}$ | $\mathbf{C_f}$ | $L_{\rm L}$ | $\mathbf{R}_{\mathrm{L}}$ | $L_1 = L_2 = L_3 = L_4$ | f       | $\mathbf{f}_{\mathrm{smax}}$ |

|---------------|------|----------------|----------------|----------------|-------------|---------------------------|-------------------------|---------|------------------------------|

| Design Values | 350V | 230V           | 50Hz           | 3.68µF         | 100mH       | 100Ω                      | 530μΗ                   | 2.25kHz | 75kHz                        |

#### IV GRID CONNECTED OPERATION

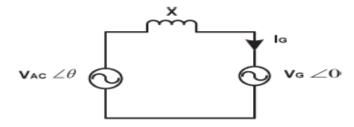

The single-line diagram of the Dual Buck Full Bridge Inverter in the grid-connected mode of operation is depicted in Fig. 5,

Fig. 5. Single-Line Diagram Representation of the Grid-Connected DBFBI Inverter.

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

ijates

ISSN 2348 - 7550

#### Fig.6 Complete Circuit and Block Diagram of Grid Connected DBFBI

The DBFBI inverter is represented by an AC source of magnitude  $V_{AC}$  and power angle  $\theta$ ,  $V_G \angle 0$  is the reference grid side voltage. The active power (P) that can be transferred from the DBFBI inverter to the grid is given as,

$$P = \frac{v_{AC}v_{C}}{x}\sin\theta \tag{10}$$

The conditions for transferring the active power alone are

$$|V_{AC}| = |V_G| \text{ and } \theta > 0$$

(11)

Where  $V_{G}$  is the Grid voltage.

In the presented setup, the DBFBI generates a voltage  $V_{AC} \angle \theta$  to meet the conditions in (11). Since inductive reactance X is constant, the active power fed to the grid only depends on  $\theta$ . As the value of  $\theta$  increases, the power fed to the grid also increases.

The reactive power (Q) that can be transferred from the DBFBI inverter to the grid is given as,

$$Q = \frac{V_G}{x} \left[ V_{AC} \cos \theta - V_G \right] \tag{12}$$

Reactive Power fed to the grid depends on the magnitude of the inverter  $|V_{AC}|$ . As the value of  $V_{AC}$  increases, the reactive power fed to the grid also increases.

#### V SIMULATION RESULTS AND DISCUSSIONS

Simulation for closed loop DBFBI has been done with the circuit parameters mentioned in Section III. In simulation - performance analysis of DBFBI with RL load in closed loop, Robustness of the control strategy, Simulation with non-linear load, Performance of the inverter during Grid connected operation has been explained.

#### a) Closed Loop with RL Load

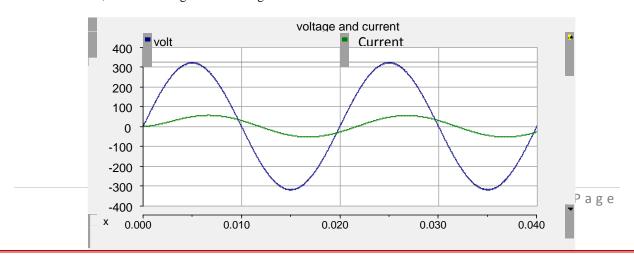

As shown in Fig. 1, closed loop DBFBI use hysteresis current controller, since we are using hysteresis current controller the switching frequency varies depending on the hysteresis band, but the advantage of using hysteresis current control is that the output quality will get improved and a naturally filtered output will be obtained from this and the output voltage THD will get improved. Output voltage and current waveform for a load of  $R=100\Omega$ , L=100mH is given in the Fig.7

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Fig. 7. Closed Loop Output Voltage and Current Waveform (Current Scale Factor = 20)

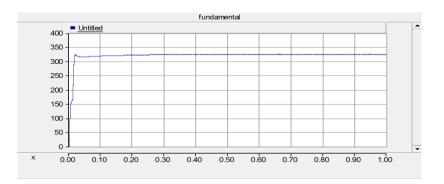

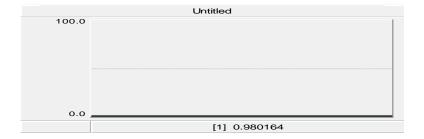

The fundamental maximum output voltage reached at a steady state value of 325.269 V and THD of the output voltage is 0.98% as seen in Fig. 8 and Fig. 9 then inverter performs well with this THD.

Fig.8 Fundamental Maximum Output Voltage Variation for closed Loop

Fig. 9. %Total Harmonic Distortion for Closed Loop

### b) Robustness of the Control Strategy

An inverter is said to be robust if and only if it can withstand or change according to the variations in the input side and the reference side respectively.

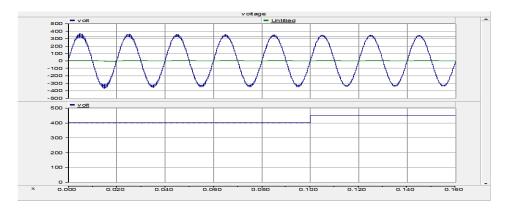

### **▶** Variation in Input Voltage or Input Voltage Disturbances

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Fig. 10. Input Voltage Disturbance and Corresponding Output Voltage

In Fig. 10, the input DC voltage is going to be changed from 400 V to 450 V but we can observe that there is no change in the output voltage and the output voltage is maintaining 325.269 V maximum output voltage, if the control strategy is not working properly we cannot achieve this.

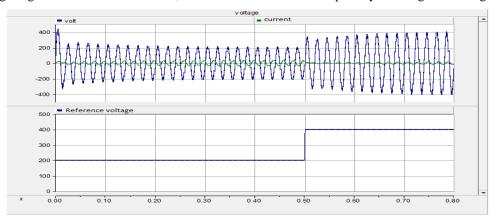

#### Variation in Reference Voltage

Inverter output voltage and the power angle will be determined according to the reference voltage, so if there is any change is given to the reference value, the inverter should have a capability to change according to it.

Fig. 11. Reference Voltage Variation and Corresponding Output Voltage

In Fig. 11, the reference voltage maximum value is changed from 200V to 400V and we can see that change in the output voltage according to the variation in reference value and that change is attained within 0.2s.

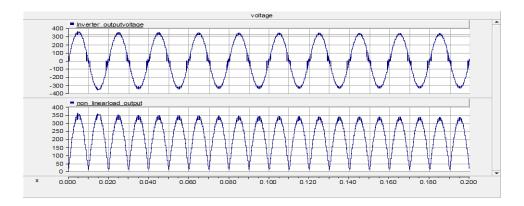

#### c) Simulation Result with Non-Linear Load

Fig. 12 shows the block diagram connection of DBFBI inverter with a non-linear load.

Fig. 12 Block Diagram for Non-Linear Load

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

ijates

Fig. 13 shows the output voltage simulation result at non-linear load with inverter output. Here we use full rectifier load as non-linear load.

Fig. 13. Inverter Output Voltage and Non-Linear Load Output Voltage

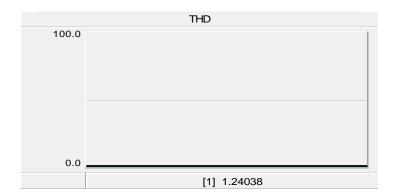

Fig. 14 shows the percentage of Total Harmonic Distortion. From this we can analyze that the DBFBI with RL load is having a THD of 0.980164%, but while using a non-linear load the THD increased to 1.24038%. So the waveform quality of the output voltage is also good at non-linear load without much change in THD.

Fig. 14. % THD for Non-Linear Load

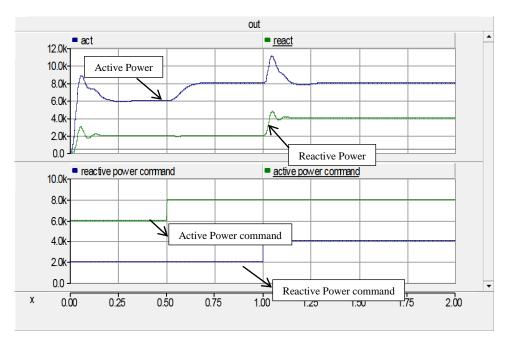

### d) Simulation Results for Grid Connected Operation

As discussed in the section IV the DBFBI inverter is connected to the grid. As we know that the grid requires both active as well as reactive power, and it may vary according to the load condition, so that the inverter should be capable of delivering both active and reactive power.

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

Fig. 15. Active and Reactive Power Change According to the Power Command

In this simulation result as shown in the Fig. 15, active power command changed from 6000W to 8000W at 0.5s from the start of simulation. Similarly, the reactive power command changed from 2000VAR to 4000VAR at 1s from the start of simulation, so the active and reactive power change accordingly.

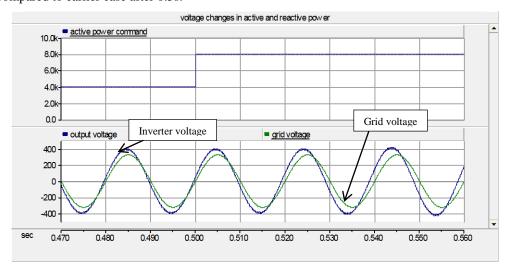

#### **Comparison of grid voltage and inverter voltage (Active Power change)**

As explained in Section 4, the active power change depends on the change in power angle  $\theta$ , while the grid side is maintained as the reference side.

In Fig. 16 the active power command changes from 4000W to 8000W at 0.5s, so the power angle  $\theta$  increases and it can be clearly seen in the figure itself that the inverter side voltage is leading with respect to grid side voltage compared to earlier case after 0.5s.

Fig. 16 Comparison of Inverter and Grid Side Voltage According to Active Power Command

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

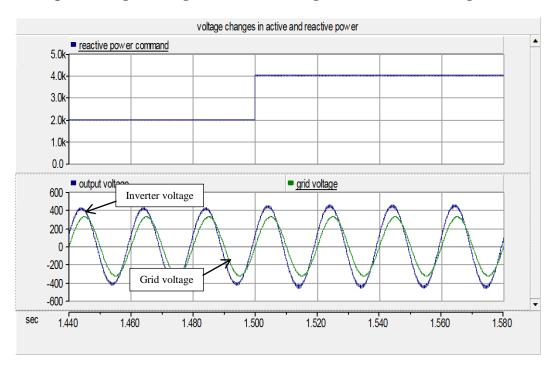

#### **Comparison of grid voltage and inverter voltage (Reactive Power change)**

Fig.17 Comparison of Inverter and Grid Side Voltage According to Reactive Power Command

The reactive power change depends on the change in the magnitude of the inverter side voltage  $V_{AC}$ , while the grid side voltage is maintained as the reference side.

In Fig. 17 the reactive power command changes from 2000VAR to 4000VAR at 1.5sec, so the magnitude of the inverter side voltage  $V_{AC}$  increases and it can be clearly seen in the figure itself that the inverter side voltage is increasing with respect to grid side voltage compared to earlier case after 1.5sec.

#### VI CONCLUSIONS

The closed loop operation of DC-AC dual buck full bridge inverter has been simulated in PSCAD and the analysis has been conducted, following are the conclusions drawn from the analysis:

In contrast to the DBHBI, the input voltage utilization rate doubles, and the voltage stress of the power device is half that in the DBHBI at the same output voltage. Compared to other inverters, the input divided capacitors do not exist in the DBFBI, so no even harmonics at the output. In comparison with the full bridge inverter, shoot through problem does not exist. All switches, diodes, and filter inductors operate at each half line cycle, so the efficiency can be improved.

The DBFBI with hysteresis current controller operates at a rated voltage of 230V and with a lower THD value of (0.98%). Robustness of the control strategy has been verified and there is no variation in the output voltage

Vol. No.5, Issue No. 03, March 2017

www.ijates.com

ijates

with input voltage variation, also the inverter will attain the output voltage according to the reference voltage. With nonlinear load there is not much change in the output voltage from the inverter side and THD is 1.24%, but earlier with RL load was 0.98%. Grid connected operations were explained and the inverter have the capability of supplying both active power as well as reactive power to the grid side without any fail. The Dual Buck Full Bridge Inverter is capable of generating a sinusoidal ac voltage of the desired frequency and magnitude without using any additional ac filter at its output terminals.

#### **REFERENCES**

- [1] F. Blaabjerg, Z. Chen, and S. B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Trans. Power Electronics.*, 19(5),1184-1194, Sep. 2004.

- [2] J. S. Lai and F. Peng, "Multilevel converters—A new breed of power converter," *IEEE Trans. Ind. Electron.*, 32(3),509–517, May/Jun. 1996.

- [3] J. Rodriguez, J. S. Lai, and F. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, 49(4),724–738, Aug. 2002.

- [4] M. Malinowski, K. Gopakumar, J. Rodriguez, and M.A. Pérez, "A survey on cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, 57(7), 2196–2206, Jul. 2010.

- [5] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, The age of multilevel converters arrives, *IEEE Ind. Electron. Mag.*, 2(2), 28–39, Jun. 2008.

- [6] R. H. Baker, "Electric Power Converter", US Patent 3867643, Feb. 1975.

- [7] M. Mezaroba, D. C. Martins, and I. Barbi, A ZVS PWM half-bridge voltage source inverter with active clamping, *IEEE Trans. Ind. Electron.*, 54(5),2665–2672, Oct. 2007.

- [8] Z. Yao, Z. Wang, L. Xiao, and Y. Yan, A novel control strategy for grid interactive inverter in grid-connected and stand-alone modes, *In Proc. IEEE APEC*, 2006, 779–783.

- [9] Adam G.P et.al. Capacitor balance issues of the Diode-clamped multilevel inverter. *IEEE Trans. on Industrial Electronics*, 55(8), 3088-3099, Dec. 2008.

- [10] Zhilei Yao, Lan Xiao and Yangguang Yan, Dual buck full-bridge inverter with hysteresis current control, *IEEE Trans. on Ind. Electronics*, 56(8), August 2009.