Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

# MODIFIED BORROW SELECT SUBTRACTOR FOR LOW POWER AND AREA EFFICIENCY

Mr.K. Upendra Raju<sup>1</sup>, Kristipati Dolika<sup>2</sup>, K Madhusudhan Reddy<sup>3</sup>, Kolle Priyanka<sup>4</sup>, Krishna Murthy Lokesh<sup>5</sup>, Kandalam Praneeth Krishna<sup>6</sup>

<sup>1</sup>Associate Professor, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India. <sup>23456</sup>B.Tech Students, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India.

#### **ABSTRACT**

Power is one of the most significant designs bound after speed, in integrated circuit. One of the basic essential components in such circuit is adder and subtractor. In order to optimize such circuits, there is need of designing proficient and low power fundamental blocks. This paper presents two architectures of modified borrow select subtractor that consume less power with increased area efficiency. The modifications carried out in the logical flow of subtraction process by using blocks with lower number of logic gates lead to a smaller number of gates, thus resulting in less device count, lower area and lower power dissipation. The synthesis and simulation results are carried out using Xilinx ISE 14.7.

Keywords: Borrow Select Subtractor, Low Power Subtractor, BSLS, Adder-Subtractor.

#### **INTRODUCTION**

The role of arithmetic circuits in all the signal processing units is of paramount importance and in which Adder-Subtractor circuit is indispensable. Adders, subtractors and multipliers are the essential building blocks of processors. Normally, subtraction is done using adder-subtractor module, which can practically result in slowing down arithmetic operation, since the same hardware has to be used for both addition and subtraction processes using additional control signals. The commonly used Ripple Borrow Subtractor (RBS) used for subtraction of unsigned numbers possesses a simple architecture. However, performance of RBS is limited by borrow propagation time incurred from Least Significant Bit (LSB) to Most Significant Bit (MSB). In other words, the delay of RBS depends on binary word length. Borrow Select Subtractor (BSLS) architecture is proposed here to overcome the limitations of existing RBS with multiple RBS circuits. This method generates partial difference and borrow using multiplexers (MUX) and the final difference and borrow is selected. As the BSLS utilizes multiple RBS circuits in it, it is proved normally area inefficient.

Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

The primary focus is on reducing area and power consumption, which is achieved by using logic blocks with fewer gates occupying less area even while aiming for same logic functionality.

### LITERATURE REVIEW

In 2010, Emam [4] proposes two novel designs of Adder/Subtractor using reversible logic gates. The first design is an implementation of two's complement Adder/Subtractor suitable for signed/unsigned numbers. The other design proposes a novel reversible gate that can work singly as a reversible Full Adder/Subtractor unit. The proposed Full Adder/Subtractor is then applied to design a reversible 4-bit ripple Adder/Subtractor.

In 2015, T. F. Tay and C. Chang [5] proposes that efficient modular adders and subtractors for arbitrary moduli are key booster of computational speed for high-cardinality Residue Number Systems as they rely on arbitrary moduli set to expand the dynamic range. This paper proposes a new unified modular adder/subtractor that possesses regular structure for any modulus. Compared to the latest modular adder/subtractor, which works for modulus in the forms of  $2^n \pm k$ , the proposed design is faster and consumes lower power for n range from 4 to 8.

In 2018, Shabeerkhan [6], proposed Power is one of the most significant designs bound after speed, in integrated circuit. One of the basic essential components in such circuit is adder and subtractor. In order to optimize such circuits, there is need of designing proficient and low power fundamental blocks. we present a new design of the full subtractor based on difference based borrow calculation. The proposed full subtractor is optimized in terms of delay, cost and power. The proposed reversible full subtractor is shown to be better than the existing design. The proposed subtractors proposed in this work will be useful in a number of digital signal processing applications.

#### **EXISTING METHOD**

The subtractor circuit analyzes the data with the help of reference signal and allows the signal to the concerned operation without changing its originality. The subtractor circuit is very useful device in signal/data processing, fast multiplier and propagating signals. Low-power IC design has become an especially vibrant area of research and development, resulting in advances in low-power fabrication processes and circuit techniques, dynamically programmable power supplies and power efficient microprocessors.

Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

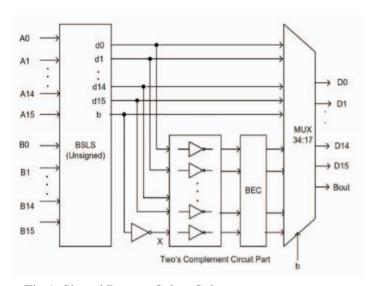

The difference between the subtrahend and the minuend is in 2's complement form when the subtrahend is greater than minuend. To convert the two's complement form into signed magnitude form, additional blocks are required. When borrow output from unsigned BSLS is 0, the result is positive. Hence, the output doesn't necessitate the conversion to signed magnitude form. Similarly, as borrow output is 1, the result is negative. Then, the output of borrow-out is complemented and 2's complement is performed on entire result in signed magnitude form. Fig. 5 depicts the signed borrow select subtractor. The 16-bit BSLS for unsigned numbers consists of five logic groups. Each group computes the difference and borrow for different number of bits. Each functional group except first group has 2 n-bit RBS, n-bit BEC and a (2n+2):(n+1) multiplexer.

B3 B2

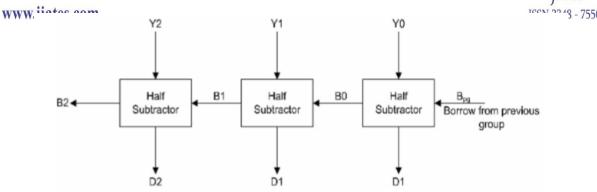

Fig.1. Signed Borrow Select Subtractor

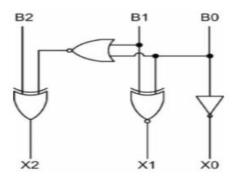

Fig.2. 2-Bit BEC

### PROPOSED METHOD

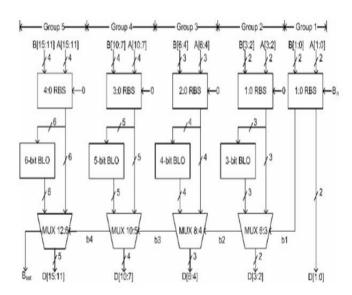

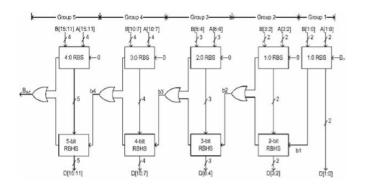

**BSLS-BLO:** The First proposed architecture replaces the second n-bit RBS and BEC-1 of BSLS using (n+1)-bit Binary-Less-One (BLO) logic in all groups. It uses Binary-Less-One (BLO) logic as shown in Fig.3. for 3-bit BLO logic. The proposed Binary-Less-One (BLO) logic accomplishes the same operation of generating the difference and borrow assuming that the Bin from the previous stage is 1. Fig.4 shows the architecture of the modified Borrow Select Subtractor circuit configured using Binary-Less-One logic (BSLS-BLO). The Binary-Less-One logic is employed in all groups except the group 1 to compute difference and borrow bits.

Vol. No. 10, Issue No. 06, June 2022

www.ijates.com

Fig.3. 3-bit Binary-Less-One (BLO)

Fig.4. Modified Borrow Select Subtractor using Binary-Less-One Logic

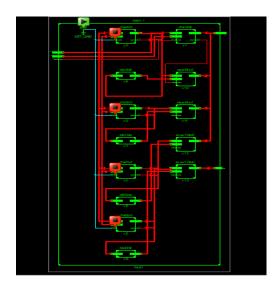

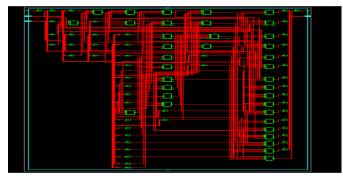

Fig.5. RTL Schematic of BSLS-BLO

**BSLS-RBHS:** A second variant of the BSLS has been proposed in this Section, which replaces the second n-bit RBS and BEC-1 of BSLS or the n-bit BLO in BSLS-BLO using n-bit ripple borrow half subtractor (RBHS) in all groups. It employs Ripple Borrow Half Subtractor (RBHS) as shown in Fig.6, as depicted for a 3-bit ripple borrow half subtractor (RBHS In this architecture, the (2n+2):(n+1) multiplexer in each group has been replaced with a OR gate. This results in reduction of number of gates. Each functional group except first group has one n-bit RBS, n-bit RBHS and an OR gate. The first group has only one two-bit RBS.Based on the borrow bit Bin generated from the previous group, the difference and borrow bit values have been computed.

Vol. No. 10, Issue No. 06, June 2022

Fig. 6. 3-bit Ripple Borrow Half Subtractor (RBHS)

Fig.7. Modified Borrow Select Subtractor using Ripple Borrow Half Subtractor

Fig.8. RTL Schematic of BSLS-RBHS

### METHODS OR TECHNIQUES USED

Xilinx Tools is a suite of software tools used for the design of digital circuits implemented using Xilinx Field Programmable Gate Array (FPGA) or Complex Programmable Logic Device (CPLD). The CAD tools enable you to design combinational and sequential circuits starting with Verilog HDL design specifications. Digital designs can be entered in various ways using the above CAD tools: using a schematic entry tool, using a hardware description language (HDL) – Verilog or VHDL or a combination of both. In this lab we will only use the design flow that involves the use of Verilog HDL.

#### **RESULT**

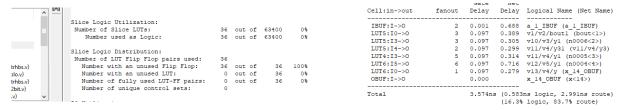

The proposed architectures have been designed under the design environment for comparing the results justifiably. The two architectures have been simulated and the area, delay and power reports obtained. These reports were compared with the expected area (by device count), delay and power and tabulated.

Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

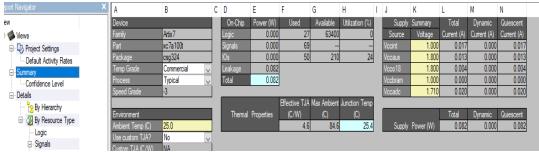

Fig.9. BSLS-BLO Area

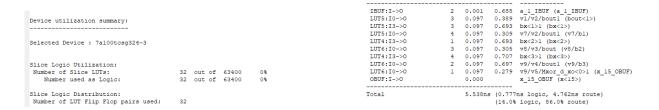

Fig.10. BSLS-BLO Delay

Fig.11. BSLS-BLO Power

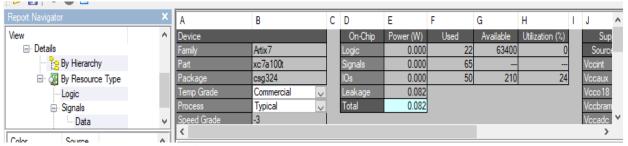

Fig.12. BSLS-RBHS Area

Fig.13. BSLS-RBHS Delay

Fig.14. BSLS-RBHS Power

#### **Table.1: COMPARISION TABLE**

| ARCHITECTURE         | DEVICE COUNT | DELAY   | POWER |

|----------------------|--------------|---------|-------|

| BSLS                 | 282          | 5.674ns | 210mW |

| BSLS-BLO (Proposed)  | 202          | 3.57ns  | 82mW  |

| BSLS-RBHS (Proposed) | 142          | 5.53ns  | 82mW  |

### CONCLUSION

Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

This paper presents modified borrow select subtractor using Borrow Less One and modified borrow select subtractor using Ripple Borrow Half Subtractor. The number of gates employed is less in both proposed architectures compared to existing architecture. On comparing these structures there is 28.36% and 49.64% reduction in device count respectively for Borrow Less One and Ripple Borrow Half Subtractor. This design approach also leads to reduced number of transistors utilized, lower area and reduced power consumption.

Since Mostly adders and subtractors are used in DSP applications which are error tolerant. By applying the concept of approximation, we can achieve better results in terms of area, power and delay.

The future research activities may include integration of the proposed DFF in complex digital systems, combining sequential and combinatorial logic. The future research activities may include integration of the proposed DFF in complex digital systems, combining sequential and combinatorial logic. The future research activities may include integration of the proposed DFF in complex digital systems, combining sequential and combinatorial logic. The future research activities may include integration of the proposed DFF in complex digital systems, combining sequential and combinatorial logic.

#### **REFERENCES**

- [1] Amit Maruti Kunjir and V S Kanchana Bhaaskaran, "A high speed borrow select 16-bit subtractor", The Patent Office Journal Appl. 2868/CHE/2014 A, Jan. 22, 2016.

- [2] L.E.M. Bckenbury and W.Shao, "Lowering Power in an Experimental RISC processor", Microprocessor and Microsystems, pp. 360-368, 2007.

- [3] V Jayaprakasan, S Vijayakumar, V S Kanchana Bhaaskaran, "Evaluation of the Conventional vs. Ancient Computation methodology for Energy Efficient Arithmetic Architecture", Int. Conf on Process Automation, Control and Computing (PACC), 2011, 20-22.

- [4] Emam, M. T., & Elsayed, L. A. A. (2010). Reversible Full Adder/Subtractor. 2010 XIth International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design (SM2ACD).

Vol. No. 10, Issue No. 06, June 2022 www.ijates.com

- [5] T. F Tay and C. Chang, "A new unified modular adder/subtractor for arbitrary moduli," 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, 2015, pp. 53-56.

- [6] Shabeerkhan "A Novel DBB (Difference Based Borrow) Subtractor for Low Power Applications", 2018, International Journal of ChemTech Research.

- [7] O. J. Bedrij, "Carry-select adder", IRE Transactions on Electronics & Computers, pp.340–344, 1962

- [8] T. Y. Ceiang and M. J. Hsiao, "Carry-Select Adder Using Single Ripple Carry Adder," Electronics Letters, V. 34, No. 22, Pp. 2101–03, Oct. 1998.

- [9] B. Ramkumar and Harish M Kittur, "Low-Power and Area-Efficient Carry Select Adder", IEEE Trans. on Very Large Scale Integration (VLSI) Systems, vol. 20, no. 2, pp.371-75, Feb. 2012.

- [10] Kore Sagar Dattatraya and V. S. Kanchana Bhaaskaran, "Modified Carry Select Adder using Binary Adder as a BEC-1,", European Journal of Scientific Research V.103, no.1, pp.156-164, Jan. 2013.

- [11] Y. Kim and L.-S. Kim, "64-Bit Carry-Select Adder with Reduced Area," Electronics Letters, Vol. 37, No. 10, pp. 614–615, May 2001.

- [12] B. Srinivasa Ragavan, B. P. Bhuvana and V. S. Kanchana Bhaaskaran, "Low power 64-bit carry select adder using modified exnor block", Journal of Engg. and Applied Sciences, Vol.10, pp. 17294, Dec, 2015.

- [13] Samiappa Sakthikumaran, S. Salivahanan, V. S. Kanchana Bhaaskaran, V. Kavinilavu, B. Brindha and C. Vinoth "A Very Fast and Low Power Carry Select Adder Circuit", 3rd International Conference on Electronics Computer Technology ICECT 2011, Pp. 273-276, April 8 10, 2011.

- [14] J. M. Rabaey, Digital Integrated Circuits A Design Perspective. Upper Saddle River, NJ:Prentice-Hall, 2001.